# This is a self-archived version of an original article. This version may differ from the original in pagination and typographic details.

Author(s): Aravind Kulkarni, Anant; Haghparast, Majid

**Title:** Identity Rules-Based Decomposition, Optimization, and Spin-Torque Modeling of Controlled V and V+ Gates for Quantum Full Adder

Year: 2024

Version: Published version

Copyright: © 2024 The Authors

Rights: CC BY 4.0

Rights url: https://creativecommons.org/licenses/by/4.0/

# Please cite the original version:

Aravind Kulkarni, A., & Haghparast, M. (2024). Identity Rules-Based Decomposition, Optimization, and Spin-Torque Modeling of Controlled V and V+ Gates for Quantum Full Adder. IEEE Access, 12, 164911-164921. https://doi.org/10.1109/access.2024.3492915

Received 22 September 2024, accepted 3 November 2024, date of publication 6 November 2024, date of current version 18 November 2024.

Digital Object Identifier 10.1109/ACCESS.2024.3492915

# **RESEARCH ARTICLE**

# Identity Rules-Based Decomposition, Optimization, and Spin-Torque Modeling of Controlled V and V+ Gates for Quantum Full Adder

ANANT ARAVIND KULKARNI<sup>©</sup>1 AND MAJID HAGHPARAST<sup>©2</sup>, (Senior Member, IEEE)

<sup>1</sup>Institute of Technology, Nirma University, Ahmedabad 382421, India

Corresponding author: Majid Haghparast (majid.m.haghparast@jyu.fi)

The work of Majid Haghparast was supported in part by the Academy of Finland under Project DEQSE 349945, and in part by Business Finland under Project TORQS 8582/31/2022.

**ABSTRACT** The quantum computing (QC) is emerging as one of the possibilities to replace the conventional computing to meet the complex computing challenges. Quantum gates are based on the quantum mechanical phenomena such as superposition and entanglement. Moreover, there are several ways to realize the reversible full adder representing one of the building blocks of the reversible computing. One of the ways to realize the reversible full adder is by using the controlled V and V+ gates. Spintronics is one of the quantum technologies to realize the reversible computing physically. Therefore, there is need of spin-torque based modelling of controlled V and V+ gates for the quantum computing applications in the reversible computing domain. In this paper, the controlled V and V+ gates are modelled for the spin-torque based qubit architecture through the optimization at elementary single-qubit rotation and two-qubit entanglement level. Therefore, the key innovation or unique contribution is to realize the controlled V and V+ gates by using the minimum number of the elementary operations (single- and two-qubits). Moreover, a quantum full adder (QFA) composed of controlled V and V+ gates, is optimized and realized with the spin-torque models of the controlled V and V+ gates to achieve fault tolerant fidelity. Therefore, the novelty is that the optimization of the controlled V and V+ gates for the reversible full adders is carried out by using the identity rules.

**INDEX TERMS** Quantum gates, quantum circuits, spin-torque, optimization.

### I. INTRODUCTION

The logic gates are the building blocks of the Boolean computing. However, there is loss of information in these gates except NOT gate. The one-bit loss of information results in KTln2 joules dissipation of the heat [1]. The K and T are Boltzmann constant and temperature respectively. Though this heat dissipation is negligible for the individual irreversible logic gates, however, it needs attention as the complexity of the computing system increases. The way out

The associate editor coordinating the review of this manuscript and approving it for publication was Alba Amato.

to get rid of the heat dissipation, is to use the reversible gates such as CNOT, Toffoli, Fredkin, controlled V, and V+. These reversible gates have one-to-one mapping from input to output. The quantum circuits made up of these reversible gates are suitable for the low-power VLSI [2]. However, the physical realization of quantum circuits for the reversible computing becomes very difficult by using the classical complementary metal oxide semiconductors (CMOS) technology due to one-to-one mapping of the inputs to the outputs utilization of the ancilla qubits and shrink in channel length of the transistor. The quantum technologies such as Quantum Dot (QD) [3], Superconducting (SC) [4], Ion Traps (IT) [5],

<sup>&</sup>lt;sup>2</sup>Faculty of Information Technology, University of Jyväskylä, 40014 Jyväskylä, Finland

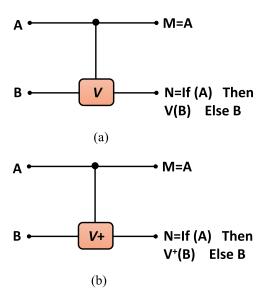

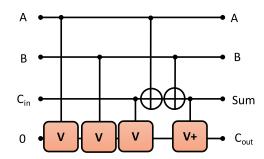

FIGURE 1. Controlled V gate (b) Controlled V+ gate.

Rydberg atoms [6], Linear Photonics (LP) [7], Non-Linear Photonics (NP) [8], and Spin-Torque (ST) [9] are promising candidates for the physical realization of the reversible computing. However, every quantum technology has a unique library of gates to realize the quantum computing and scalability issues which need to be addressed. The spin-torque [8] based technology has the advantage of operating at room temperature in comparison to superconducting based qubit architecture. Therefore, in this paper, the modelling of the controlled V and controlled V+ gates for the spin-torque based qubit architecture [10], is presented in terms of their decomposition, reduction, and optimization [11], [12]. Moreover, the models for the controlled V and controlled V+ are utilized to realize the quantum full adder [13], [14]. The fidelities of the existing work are presented in Table 1.

TABLE 1. Existing work.

| Existing Work              | Fidelity (%)  |

|----------------------------|---------------|

| 2-Toffoli Full Adder [16]  | 97.65         |

| 1-Toffoli Full Adders [14] | (98.21-98.34) |

The key contributions of the proposed work in a pointwise manner.

- Decomposition of the controlled V ad V+ gates at elementary single-qubit rotation and two-qubit entanglement level for the spin-torque based qubit architecture.

- Modelling of the controlled V and controlled V+ gates with the help of spin-torque based elementary single qubit rotation and two-qubit entanglement.

- The fidelity of the controlled V and V+ obtained is more than 99%

- The controlled V and V+ gates based reversible full adder is realized using the spin-torque models for the controlled V and controlled V+ gates.

FIGURE 2. Spin-torque-based *n*-qubit reconfigurable architecture.

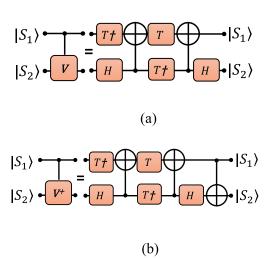

FIGURE 3. Elementary-level decomposition of (a) Controlled V gate (b)Controlled V+ gate.

FIGURE 4. Elementary single- and two-qubit rotation-level decomposition of Controlled V gate.

The paper is divided in five sections including this introduction section. The controlled V and V+ gates and their significance are presented in section II. The spin-torque based qubit architecture [10] is discussed in section III. The decomposition of the controlled V and V+ are presented and the spin-state evolution of controlled V gate is discussed in section IV. The identity rules-based optimization of the controlled V and V+ gates, is carried out in section V. The controlled V and V+ gates based QFA is implemented in section VI followed by conclusion in section VII.

**FIGURE 5.** Density matrix evolution for the input configurations  $|S_1\rangle(z=1)$  and  $|S_4\rangle(z=1)$ .

**FIGURE 6.** Density matrix evolution for the input configurations  $|S_1\rangle(x=1)$  and  $|S_4\rangle(x=1)$ .

**FIGURE 7.** Density matrix evolution for the input configurations  $|S_1\rangle(y=1)$  and  $|S_4\rangle(y=1)$ .

# II. CONTROLLED V AND V+ GATES

The V and V+ gates are represented by a  $2 \times 2$  matrix

$$V = \begin{bmatrix} \frac{1+i}{2} & \frac{1-i}{2} \\ \frac{-1-i}{2} & \frac{1+i}{2} \end{bmatrix}$$

(1)

$$V^{+} = \begin{bmatrix} \frac{1-i}{2} & \frac{1+i}{2} \\ \frac{1+i}{2} & \frac{1-i}{2} \end{bmatrix}$$

(2)

The V+ is the Hermitian conjugate of V and called  $\sqrt{NOT}$ . The properties of these gates are as follows.

$$V \times V = NOT$$

$V \times V^{+} = V^{+}XV = I$

$V^{+} \times V^{+} = NOT$

The controlled V and V+ are represented by the following matrices.

$$V = \frac{1+i}{2} \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & -i \\ 0 & 0 & -i & 1 \end{bmatrix}$$

(3)

FIGURE 8. Identity rule-based optimization of Controlled V gate.

$$V^{+} = \frac{1-i}{2} \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & i \\ 0 & 0 & i & 1 \end{bmatrix}$$

(4)

The truth tables for the (V, V+) and Controlled (V, V+) are given in Table 2 and Table 3, respectively. v, V, w, and W are intermediate states.

FIGURE 9. Identity rule-based optimization of Controlled V+ gate.

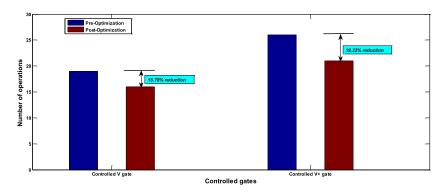

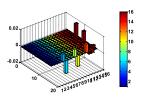

FIGURE 10. Post-optimization percentage reduction in number of operations.

**FIGURE 11.** Density matrix evolution for the input configurations  $|S_1|(x=1)$  and  $|S_4|(z=1)$ .

FIGURE 12. Density matrix evolution for the input configurations  $|S_1\rangle(z=1)$  and  $|S_4\rangle(z=1)$ .

TABLE 2. Truth Table (V and V+ gates).

| A (Input) | M (V gate) | M (V+ gate) |

|-----------|------------|-------------|

| 0         | V          | W           |

| 1         | V          | W           |

| v         | 1          | 0           |

| V         | 0          | 1           |

| W         | 0          | 1           |

| W         | 1          | 0           |

TABLE 3. Truth Table (controlled V and controlled V+ Gates).

| A<br>(Input) | B<br>(Input) | M<br>(Output) | N (Output)-<br>V gate | N<br>(Output)-<br>V gate |

|--------------|--------------|---------------|-----------------------|--------------------------|

| 0            | X            | 0             | X                     | X                        |

| 1            | 0            | 1             | v                     | W                        |

| 1            | 1            | 1             | V                     | W                        |

| 1            | v            | 1             | 1                     | 0                        |

| 1            | V            | 1             | 0                     | 1                        |

| 1            | W            | 1             | 0                     | 1                        |

| 1            | W            | 1             | 1                     | 0                        |

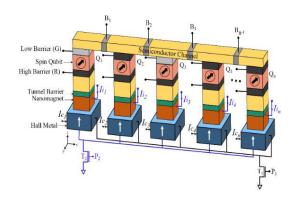

# III. SPIN TORQUE BASED QUBIT ARCHITECTURE

The ST-based qubit architecture is shown in Fig. 2. Each arm of the architecture represents a single spin-qubit associated with the low and high barriers on either side. The semiconductor channels are present between the qubits. The barrier height modulation helps to make the architecture reconfigurable. The Hall metal-nanomagnet-tunnel barrier assembly injects the spin polarized electrons (x-/y-/z-directed) into the semiconductor channel. The injected electrons with velocity  $\nu$  crossing through the semiconductor channel reach the single spin-qubit and apply the spin-torque to rotate the qubit's spin-state to a desired state. The similar mechanism is applicable for the two-qubit rotation. The entire mechanism is modelled with the help of transmission and reflection coefficients in the one-dimensional reconfigurable spin-torque based qubit-architecture.

The transmission and reflection coefficients of the spin-torque based architecture are modelled as transmission [10] and reflection coefficient matrices in equation (5)

**FIGURE 13.** Density matrix evolution for the input configurations  $|S_1|(x=-1)$  and  $|S_4|(y=1)$ .

FIGURE 14. Controlled V and V+ gate based QFA [11].

and (6), respectively,

$$t^{(2)} = \frac{1}{(1 + i4\Omega l)I + i\tilde{S}(\Omega - (i4\Omega^2 l(e^{i2kx_0} - 1)))}$$

(5)

where,  $\tilde{S}$  is the standard basis matrix,  $l = \frac{\Gamma_{Rfl}}{J}$ ,  $\Omega = J/\hbar v$ , and v is the velocity of the electron,  $\Gamma_{Rfl}$  is the height of the

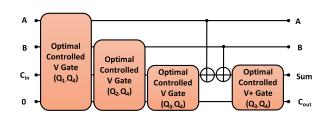

FIGURE 15. Optimal Controlled V and V+ gate based QFA.

reflection barrier G, J is the hyperfine or exchange interaction, and  $x_0$  is the distance of the qubit from the barrier, and  $\hbar$  is reduced Plank's constant.

The reflection matrix is

$$r^{(2)} = t^{(2)} - I, (6)$$

where I is the identity matrix.

FIGURE 16. Optimal decomposition of QFA.

The generalized reflection matrix  $R_F^{(2)}$  based on equations (5) and (6) is provided in equation (7) as follows:

$$R_F^{(2)} = r^{(2)} - e^{i2kx_0}t^{(2)} \left[ I_{2^{n+1}} + e^{i2kx_0}I_{2^{n+1}}R_0 \right]^{-1} I_{2^{n+1}}t^{(2)},$$

(7)

where,  $R_0$  matrix represents the reflection barrier, and I is the identity matrix for the n-qubit architecture. The reflection matrix for the two-qubit interaction on qubits  $Q_1$  and  $Q_2$  is given in equations (6) and (7), respectively, and the overall reflection matrix at the injection side barrier is given in equation (8).

$$R_{F_{1}}^{(2)} = r_{1}^{(2)} - e^{i2kx_{0}}t_{1}^{(2)} \left[I_{2^{n+1}} + e^{i2kx_{0}}I_{2^{n+1}}R_{0}\right]^{-1}I_{2^{n+1}}t_{1}^{(2)}$$

$$(8)$$

$$R_{F_{2}}^{(2)} = r_{2}^{(2)} - e^{i2kx_{0}}t_{2}^{(2)} \left[I_{2^{n+1}} + e^{i2kx_{0}}I_{2^{n+1}}R_{F_{1}}^{(2)}\right]^{-1}I_{2^{n+1}}t_{2}^{(2)}$$

$$(9)$$

$$R_{F_{b}}^{(2)} = r_{b}^{(2)} - e^{i2kx_{12}}t_{b}^{(2)} \left[I_{2^{n+1}} + e^{i2kx_{12}}I_{2^{n+1}}R_{F_{2}}^{(2)}\right]^{-1}I_{2^{n+1}}t_{b}^{(2)}$$

The subscripts 1, 2, and  $^{(2)}$  represent qubits  $Q_1, Q_2$ , and second order matrix, respectively.

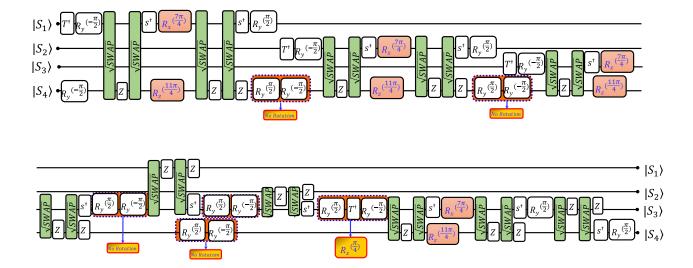

# IV. DECOMPOSTION OF CONTROLLED V AND V+ GATES AND SPIN STATE EVOLUTION OF CONTROLLED V GATE

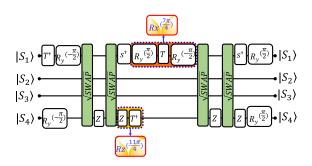

The gate level quantum circuits for the controlled V and V+ are shown in Fig.3(a) and Fig.3(b). The spin-torque based modelling of controlled V and V+ gates need their decomposition at the elementary single qubit rotation and two-qubit entanglement. Therefore, the elementary level quantum circuit of the controlled V is shown in Fig.4.

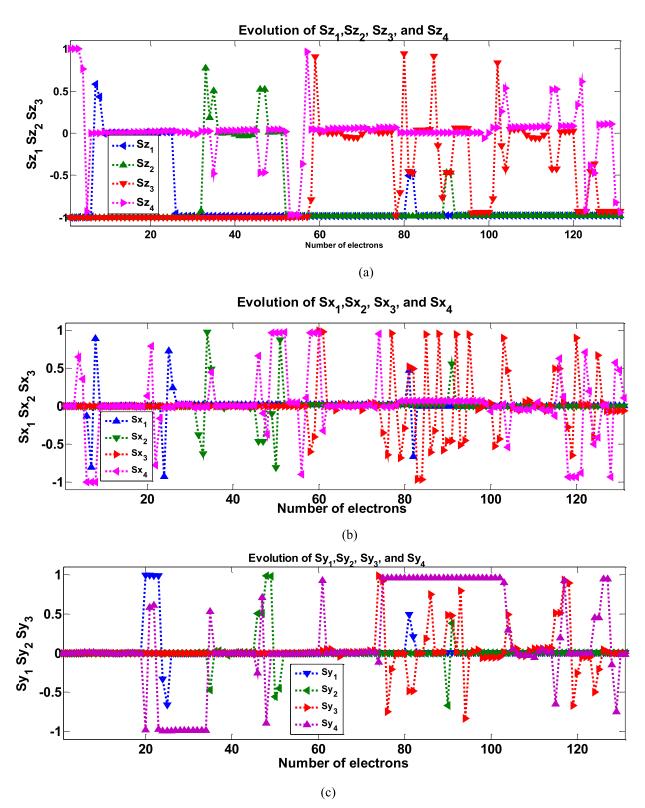

The quantum gates state evolution from the initial state to final state is represented by the density matrix. The density matrix has two components i.e. Real and Imaginary. A density matrix is defined as a  $2\times 2$  matrix, which is a linear combination of the unit/identity matrix and Pauli matrices  $\sigma_x$ ,  $\sigma_y$ , and  $\sigma_z$  as

$$\rho = \frac{1}{2}(I + \bar{a}\bar{\sigma})$$

The coefficient  $\bar{a}$  is known as the Bloch vector and is equal to

$$\bar{a} = Tr(\rho \bar{\sigma})$$

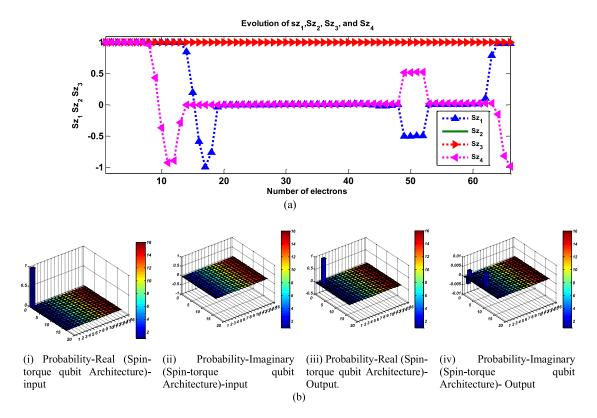

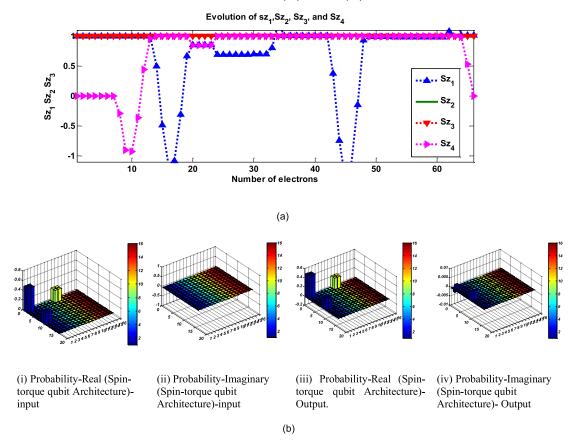

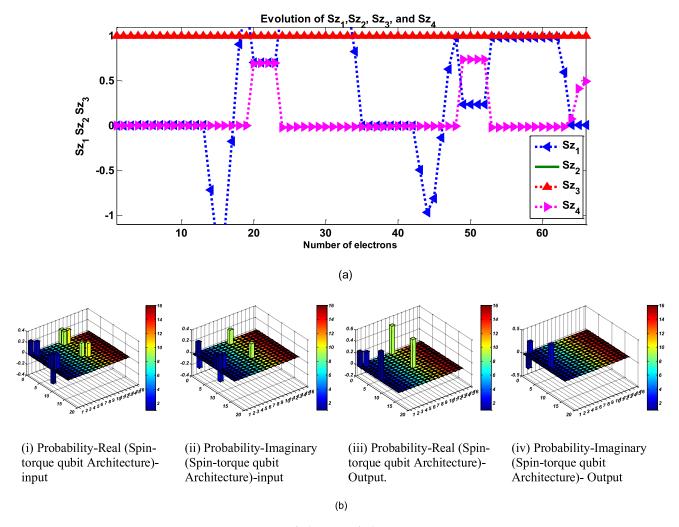

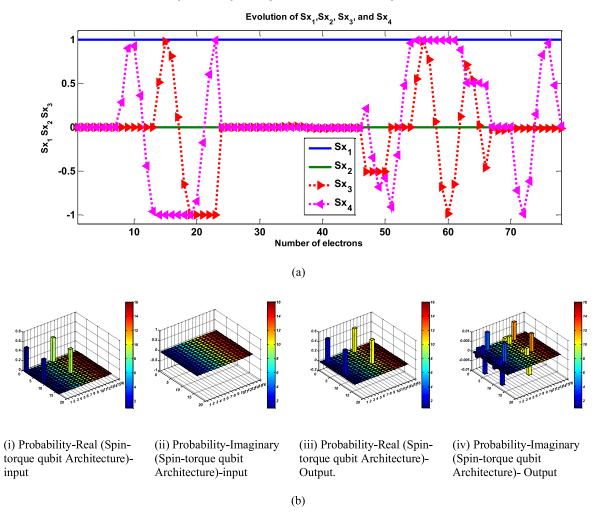

The density matrix evolution for the input state  $|1001\rangle$  and output state for controlled V gate is shown in Figure 5. The qubit state evolution along the z-axis is shown in Figure 5(a), 6(a), and 7(a). The state evolution along the z-axis is based on the sequence of single-qubit and two-qubit rotations representing the controlled V-gate as shown in figure 4. The spin state and density matrix evolution of the controlled V gate for the input configurations  $|S_1\rangle(z=1)$  and  $|S_4\rangle(z=1)$  is shown in Fig.5 (a) and (b),  $|S_1\rangle(x=1)$  and  $|S_4\rangle(x=1)$  is shown in Fig.7 (a) and (b).

# V. IDENTITY RULES TO OPTIMIZE THE CONTROLLED V AND V + GATES

The elementary single-qubit and two-qubit based reduced decomposition of the controlled V gate is shown in Fig.4. The quantum library utilized for the elementary decomposition is  $\{R_x, R_y, R_z, \sqrt{SWAP}\}$  for the reduced decomposition. The reduced decomposition presented is required to be optimized to decrease the numeral of operations. The identity rule-based decomposition [11] is utilized to optimize the elementary decomposition of the Controlled V gate. The identity rule [11] is given as below.

$$R_A^{(\theta)} = R_B^{(\frac{\pi}{2})} . R_C^{(\theta)} . R_B^{(-\frac{\pi}{2})}$$

(11)

FIGURE 17. Spin state evolution (a) z-component (b) x-component (c) y-component.

The quantum library utilized for the realization of the optimal decomposition of the controlled V gate is  $\{R_x, R_y, R_z, \sqrt{SWAP}\}$ . The identity rules-based optimal decomposition of the controlled V and controlled

V+ gates are presented in Fig. 8 and Fig. 9, respectively. The number of operations is reduced from 19 to 16 and from 26 to 22 for the controlled V and controlled V+, respectively. The bar chart for the

(ii) Probability-Imaginary (Spin-torque qubit Architecture)-input

(iii) Probability-Real (Spin-torque qubit Architecture)- Output.

(iv) Probability-Imaginary (Spin-torque qubit Architecture)- Output

FIGURE 18. Density matrix evolution of the QFA for the input state 1110.

optimization of controlled V and controlled V+, is shown in Fig. 10.

The comparison for the reduction in number of quantum operations (single-qubit and two-qubits) for the controlled V and controlled V+, is shown in figure 10. The number of operations required for realizing controlled V gate is 19 and 16, respectively for the pre- and post-optimization realization. The process of optimization is presented in figure 8. Similarly, the number of operations required for realizing controlled V+ gate is 26 and 22, respectively for the pre- and post-optimization realization. The optimization is based on the identity rules [11].

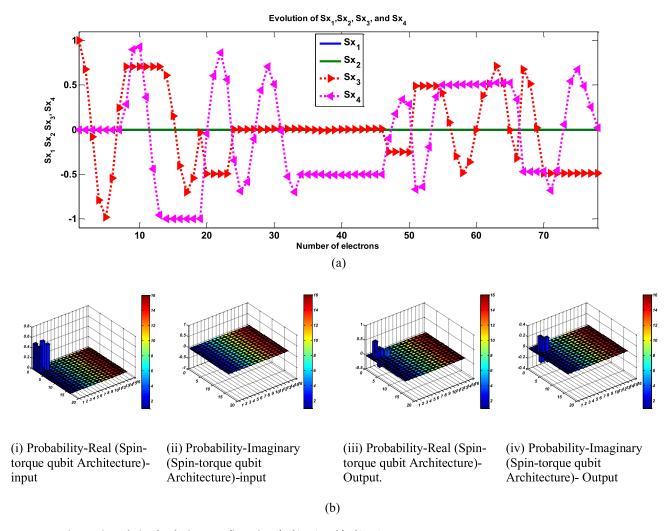

The post-optimization spin state and density matrix evolution of the controlled V+ gate for the input configurations  $|S_1\rangle(z=1)$  and  $|S_4\rangle(z=1)$  is shown in Fig.11 (a) and (b),  $|S_1\rangle(x=1)$  and  $|S_4\rangle(z=1)$  is shown in Fig.12 (a) and (b), and  $|S_1\rangle(x=-1)$  and  $|S_4\rangle(y=1)$  is shown in Fig.13 (a) and (b).

The fidelity comparison for the pre- and post-optimization of the controlled V and controlled V+ gates is given in the Table 4.

**TABLE 4. Fidelity comparison.**

| Gate       | State | Fidelity       |                |                | %              |              |

|------------|-------|----------------|----------------|----------------|----------------|--------------|

|            |       |                |                |                |                | Reduction    |

|            |       |                |                |                |                | in execution |

|            |       |                |                |                |                | time due to  |

|            |       |                |                |                |                | optimization |

|            |       | Pre- Post-     |                | 20.30%         |                |              |

|            |       | Optimization   |                | Optimization   |                |              |

|            |       | $\mathbf{Q}_1$ | $\mathbf{Q}_2$ | $\mathbf{Q}_1$ | $\mathbf{Q}_2$ |              |

| Controlled | 00>   | 99.74          | 99.76          | 99.73          | 99.78          |              |

| V          | 01>   | 99.71          | 99.75          | 99.69          | 99.77          |              |

|            | 10>   | 99.61          | 99.67          | 99.60          | 99.68          |              |

|            | 11>   | 99.62          | 99.70          | 99.61          | 99.71          |              |

| Controlled |       | $\mathbf{Q}_3$ | $Q_4$          | $\mathbf{Q}_3$ | $\mathbf{Q}_4$ | 25.30%       |

| V+         | 00>   | 99.74          | 99.67          | 99.72          | 99.73          |              |

|            | 01>   | 99.71          | 99.61          | 99.69          | 99.68          |              |

|            | 10>   | 99.95          | 99.46          | 99.49          | 99.61          |              |

|            | 11>   | 99.52          | 99.55          | 99.60          | 99.58          |              |

# **VI. QUANTUM FULL ADDER**

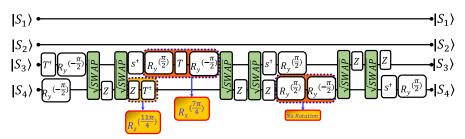

The controlled V and V+ based quantum full adder (QFA) [11] is shown in Fig. 14. It consists of 03 controlled V gates, 01 controlled V+ gate, and 02 CNOT gates.

**TABLE 5.** Comparison.

| Existing Work  | Fidelity (%)  |

|----------------|---------------|

| 2-Toffoli Full | 97.65         |

| Adder [16]     |               |

| 1-Toffoli Full | (98.21-98.34) |

| Adders [14]    |               |

| Proposed work  | 97.64         |

The quantum circuit is further modified by placing the controlled V and V+ gates by their optimal counterparts (see Fig. 15) presented in the previous section. However, the circuit still needs further optimization. The elementary level decomposition of the QFA is shown Fig. 16. The number of operations due to optimization is reduced from 83 to 71.

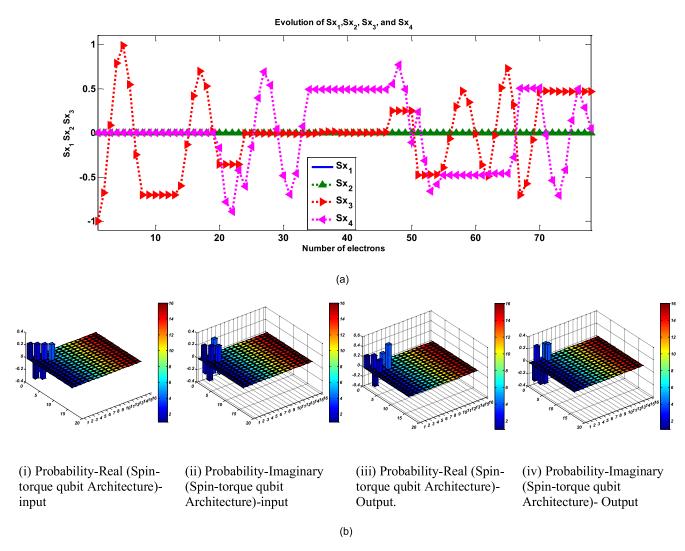

The spin state evolution of the input 1110 before quantum circuit optimization, is shown in Fig. 17.

The [15] presented the foundation for the manipulation of the quantum information using spin-torque in terms of elementary single qubit rotation and two-qubit entanglement. Also, the realization of the controlled NOT gate with fault tolerant fidelity was carried out. The spin-torque models for the quantum gates like CNOT, Toffoli, and Fredkin were utilized for the reversible Boolean computing in [16]. Also, the optimization of the quantum circuits for the reversible computing is proposed in [16]. The authors observed that there is need to utilize the quantum circuits with reduced quantum cost for the spin-torque based reversible computing. Therefore, authors investigated the performance of the 1-Toffoli reversible (quantum) full adders in [14]. The fidelities are compared as 97.65, (98.34%-98.21%), and 97.64 for the 2-Toffoli full adder, 1-Toffoli full adder, and controlled V and V+ gate based full adder, respectively. The comparison is presented in the Table 5.

The density matrix evolution for the input state 1110 is shown in Fig. 18.

# VII. CONCLUSION

The performance of QFA is investigated with the help of optimal spin-torque based models of controlled V and V+ gates. The results in terms of number of elementary operations required, number of electrons required to realize the QFA, fidelity, and probability help to realize reversible computing

with the controlled V and V+ gates as building blocks for the reversible computing applications.

# **ACKNOWLEDGMENT**

The authors would like to thank the Institute of Technology, Nirma University, Ahmedabad, India, and the University of Jyväskylä, Finland, for supporting this work.

### **REFERENCES**

- [1] R. Landauer, "Irreversibility and heat generation in the computing process," *IBM J. Res. Develop.*, vol. 5, no. 3, pp. 183–191, Jul. 1961.

- [2] C. H. Bennett, "Logical reversibility of computation," IBM J. Res. Develop., vol. 17, no. 6, pp. 525–532, Nov. 1973.

- [3] C. Kloeffel and D. Loss, "Prospects for spin-based quantum computing in quantum dots," *Annu. Rev. Condens. Matter Phys.*, vol. 4, no. 1, pp. 51–81, Apr. 2013.

- [4] S. Bravyi, O. Dial, J. M. Gambetta, D. Gil, and Z. Nazario, "The future of quantum computing with superconducting qubits," *J. Appl. Phys.*, vol. 132, no. 16, pp. 1–20, Oct. 2022.

- [5] J. Durandau, J. Wagner, F. Mailhot, C.-A. Brunet, F. Schmidt-Kaler, U. Poschinger, and Y. Bérubé-Lauzière, "Automated generation of shuttling sequences for a linear segmented ion trap quantum computer," *Quantum*, vol. 7, p. 1175, Nov. 2023.

- [6] C. T. Fancher, D. R. Scherer, M. C. St. John, and B. L. S. Marlow, "Rydberg atom electric field sensors for communications and sensing," *IEEE Trans. Quantum Eng.*, vol. 2, pp. 1–13, 2021.

- [7] M. Karácsony, L. Oroszlány, and Z. Zimborás, "Efficient qudit based scheme for photonic quantum computing," 2023, arXiv:2302.07357.

- [8] W. E. Salazar, O. Calderón-Losada, and J. H. Reina, "Linear-nonlinear duality for circuit design on quantum computing platforms," 2023, arXiv:2310.20416.

- [9] J. Qin, B. Sun, G. Zhou, T. Guo, Y. Chen, C. Ke, S. Mao, X. Chen, J. Shao, and Y. Zhao, "From spintronic memristors to quantum computing," ACS Mater. Lett., vol. 5, no. 8, pp. 2197–2215, Jul. 2023.

- [10] A. Kulkarni, S. Prajapati, and B. K. Kaushik, "Transmission coefficient matrix modeling of spin-torque-based n-Qubit architecture," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 26, no. 8, pp. 1461–1470, Aug. 2018, doi: 10.1109/TVLSI.2018.2814041.

- [11] C.-C. Lin, A. Chakrabarti, and N. K. Jha, "Optimized quantum gate library for various physical machine descriptions," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 21, no. 11, pp. 2055–2068, Nov. 2013, doi: 10.1109/TVLSI.2012.2227518.

- [12] H. C. Watanabe, R. Raymond, Y.-Y. Ohnishi, E. Kaminishi, and M. Sugawara, "Optimizing parameterized quantum circuits with free-axis single-qubit gates," *IEEE Trans. Quantum Eng.*, vol. 4, pp. 1–16, 2023.

- [13] M. Mohammadi. (2015). Behavioral Description of Quantum V and V+ Gates To Design Quantum Logic Circuits. [Online]. Available: https://www.academia.edu

- [14] A. Kulkarni, M. Haghparast, and B. K. Kaushik, "Optimization and performance investigation of 1-Toffoli gate quantum full adders for spintorque-based n-qubit architecture," *Opt. Quantum Electron.*, vol. 56, no. 1, pp. 1–20, Jan. 2024.

- [15] B. Sutton and S. Datta, "Manipulating quantum information with spin torque," Sci. Rep., vol. 5, no. 1, p. 17912, Dec. 2015.

- [16] A. Kulkarni, S. Prajapati, S. Verma, and B. K. Kaushik, "Optimal Boolean logic quantum circuit decomposition for spin-torque-based *n*-qubit architecture," *IEEE Trans. Magn.*, vol. 54, no. 10, pp. 1–9, Oct. 2018.

ANANT ARAVIND KULKARNI received the B.E. degree in electronics engineering from the Shri Guru Gobind Singhji Institute of Engineering and Technology, Nanded, India, in 2002, the M.Tech. degree in electrical engineering from Uttar Pradesh Technical University, Lucknow, India, in 2009, the M.Tech. degree in microelectronics and very-large-scale integration design from the Technocrats Institute of Technology, Bhopal, India, in 2013, and the Ph.D. degree from

the Indian Institute of Technology Roorkee, India, in 2020. Afterward, he worked as an Assistant Professor at MBES's College of Engineering Ambajogai, Maharashtra, India, and an Assistant Professor at Agnel Charities' Fr. C. Rodrigues Institute of Technology, Vashi, Navi (New) Mumbai, Maharashtra, India. At present, he is working as an Assistant Professor at Institute of Technology, Nirma University, Ahmadabad, Gujarat, India. His research interests include spintronics based devices, circuits, and computing. He is a reviewer of IEEE Transactions on Electron Devices, Quantum Information Processing, Memories - Materials, Devices, Circuits and Systems and IET-Ouantum Communications.

MAJID HAGHPARAST (Senior Member, IEEE) is currently a Research Scientist with the University of Jyväskylä, Jyväskylä, Finland. He has been a supervisor/advisor of more than ten Ph.D. and 150 M.Sc. students. He is an invited referee for more than 30 prestigious journals. His research interest includes quantum computing, where he has been involved in different projects. He is an Editorial Board Member of *Cluster Computing* (Springer), *Journal of Computational Electronics*

(Springer), and Optical and Quantum Electronics (Springer).