# Tunnel junction thermometry on three-dimensional phononic crystals

Master's thesis, December 19, 2018

Author:

EMMI KIRJANEN

Supervisor:

Ilari Maasilta

# Abstract

Kirjanen, Emmi Tunnel junction thermometry on three-dimensional phononic crystals Master's thesis Department of Physics, University of Jyväskylä, 2018, 80 pages.

In this work three-dimensional periodic nanostructures, phononic crystals to be more exact, have been studied. Phononic crystals are analogous to photonic crystals. They can modify lattice vibrations such as sound and heat in a similar manner like photonic crystals affect light. Depending on the structure and the materials some frequencies can travel faster or slower, and some frequency ranges can be completely blocked. Blocked frequency ranges are called energy gaps as vibrations are not allowed to have those energies. Phononic crystals have a wide range in applications such as thermal insulation or contact, or selecting or guiding specific frequencies.

At low temperatures, the importance of thermal management is even more essential compared to room temperature. In addition, the frequency range of thermal phonons is modified. Because of this, this work focused on effects that are present at low temperatures. This in turn restricts the phononic crystal sample period close to nano- and micrometer range, and in addition, the measurement system for thermal conduction should be suitable for low temperatures. As planned for the measurements, nanofabricated tunnel junctions could serve as a local thermometer and a heater. Tunnel junctions are highly sensitive to temperature and their theory is well known and thermometry applications are widely used. A new challenge in this work is how to fabricate such a delicate system on top of a rough crystal surface.

There has already been notable breakthroughs with two-dimensional phononic crystals. In turn, in this project the scope is three-dimensional phononic crystals with selected fabrication techniques. The techniques are a combination of multiple previously studied methods. First, a negative photoresist and UV-lithography are used to make a template structure which in turn is used to control the crystal size and position. The crystal itself was made by utilizing colloidal crystallization from sub-micron sized polystyrene spheres. It was noticed that crystals formed mostly in the patterned sites leaving the photoresist surface clean. This makes the following metal deposition steps easier, as misplaced spheres could hinder the process. For the tunnel junction fabrication, a new positive photoresist layer was deposited and then patterned with laser lithography. SINIS tunnel junctions were evaporated by using two-angle deposition. In the junction aluminum served as the superconductor (S), copper as the normal metal (N), and aluminum oxide between them as the insulator

(I). The junction deposition was found to be successful even directly on top of the crystals when using wide and thick enough wiring.

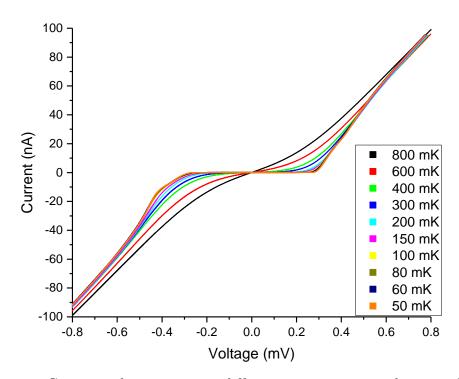

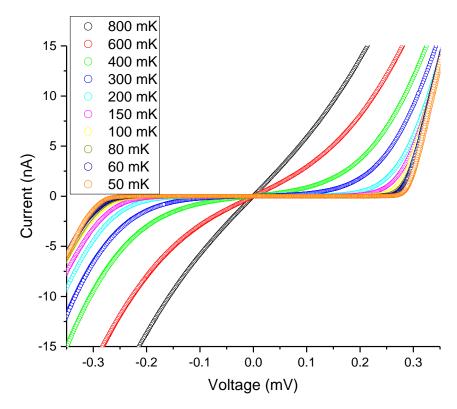

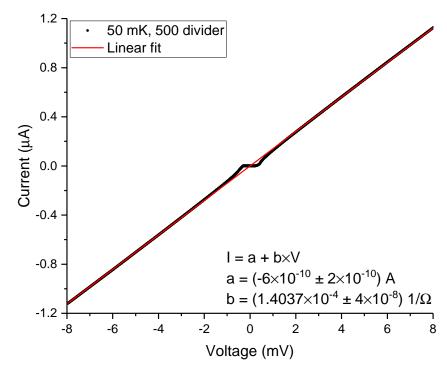

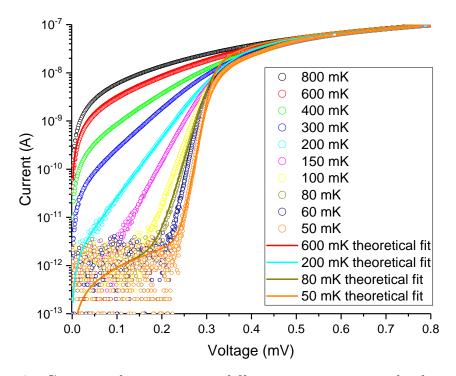

Measurements that were carried out at low temperatures confirmed that the tunnel junction fabrication was successful, by the study of the characteristic current-voltage curves. The junctions would thus be suitable to be used as thermometers. In the first measurement, there was some nonideal behavior present. However, such effects were not repeated, and unfortunately, their cause is still not fully known. Nevertheless, the second measurement was in good agreement with theory in the whole voltage range. Thermal conduction measurements were unfortunately not yet carried out, but the advancements in this thesis should make them possible in the near future. Also, possibilities for a control sample have been investigated.

Keywords: Thesis, colloidal crystallization, polystyrene, phononic crystals, SINIS tunnel junction

# Tiivistelmä

Kirjanen, Emmi Tunneliliitosten käyttäminen lämpömittarina kolmiulotteisilla fononikiteillä Pro gradu -tutkielma Fysiikan laitos, Jyväskylän yliopisto, 2018, 80 sivua

Tässä työssä on tutkittu kolmiulotteisia periodisia nanorakenteita, tarkemmin sanottuna fononikiteitä. Fononikiteet voivat muokata kiteessä liikkuvia värähtelyitä, eli ääntä ja lämpöä, samaan tapaan kuin fotonikiteet vaikuttavat valoon. Riippuen kiteen rakenteesta ja materiaaleista, jotkin taajuudet voivat kulkeutua paremmin tai huonommin, tai jotkin niistä voivat olla täysin kiellettyjä kiteen sisällä. Jälkimmäistä tapausta kutsutaan energia-aukoksi, sillä fononeilla ei voi olla kyseisiä energioita. Fononikiteitä voidaan soveltaa esimerkiksi hyvän tai huonon lämmönjohtavuuden saavuttamiseksi, tiettyjen värähtelytaajuuksien vahvistamiseksi tai poistamiseksi, tai värähtelyjen ohjaamiseksi.

Matalissa lämpötiloissa lämmönjohtumisen kontrolloinnin tärkeys korostuu ja termisten fononien taajuusalue on pienempi verrattuna korkeampiin lämpötiloihin, joten tässä työssä ollaankin keskitytty matalissa lämpötiloissa havaittaviin efekteihin. Tämä asettaa näytteen periodin nano-mikrometrialueelle ja lämmönjohtumiseen käytettävän mittasysteemin tulisi olla mataliin lämpötiloihin soveltuva. Mittauksissa nanovalmistetut tunneliliitokset toimisivat lokaalina lämmittimenä ja lämpömittarina, joita voitaisiin käyttää kiteen ominaisuuksien tutkimiseen. Tunneliliitoksien herkkä lämpötilakäyttäytyminen on hyvin tunnettu ilmiö ja niitä ollaan käytetty paljon esimerkiksi kalvojen tutkimuksessa. Uutena haasteena kuitenkin on, miten kyseisten herkkien rakenteiden valmistaminen luonnistuu kolmiulotteisen pinnan päälle.

Kaksiulotteisten fononikiteiden osalta on jo tehty huomattavia edistysaskelia, joten tässä työssä on keskitytty vain kolmiulotteisten kiteiden valmistamiseen valitulla menetelmällä. Valmistusprosessissa on yhdistetty useita aiemmin tutkittuja menetelmiä. Ensin kiteelle tehtiin negatiivisesta fotoresististä sen sijaintia ja kokoa rajoittava rakenne UV-litografian avulla puhdistetun piipalan päälle. Itse kide valmistettiin itsejärjestyvyyttä hyödyntäen kolloidikiteytyksellä polystyreenipalloista, joiden halkaisija oli satojen nanometrien luokkaa. Kiteytysprosessissa havaittiin, että polystyreenipallot hakeutuvat mieluiten niille varattuihin kohtiin ja resistin pinta jää useimmiten hyvinkin puhtaaksi, mikä mahdollistaa metalloinnin tekemisen näytteen päälle. Metallisten liitosten tekemistä varten näytteen päälle levitettiin uusi, myöhemmin poistettava resistikerros, mihin valotettiin laser-litografialla haluttu kuvio.

Kuvioidun resistin ja kahden kulman höyrystyksen avulla pyrittiin valmistamaan pari SINIS tunneliliitoksia. Liitoksessa alumiini toimi suprajohteena (S) ja kupari normaalimetallina (N), ja höyrystyksien välissä alumiinin pintaan muodostettu alumiinioksidi toimi eristeenä (I). Höyrystyksistä havaittiin, että johtimet onnistuivat suoraan kiteen päälle, mikäli ne olivat tarpeeksi leveitä ja jos metallia höyrystettiin tarpeeksi paksulti.

Matalissa lämpötiloissa suoritetut mittaukset vahvistivat valmistetut metalloinnit tunneliliitoksiksi niiden tunnusomaisten virta-jännite-käyrien perusteella. Liitokset olisivat siis soveltuvia käytettäviksi lämpötilan mittaamiseen. Ensimmäisissä mittauksissa havaittiin kuitenkin myös poikkeuksellista käyttäytymistä, minkä lähteitä ei valitettavasti vielä ymmärretä. Efektiä ei kuitenkaan saatu toistettua toisissa mittauksissa, mitkä puolestaan noudattivat teoriaa huomattavan hyvin koko jännitealueella. Lämmönjohtumismittauksia ei valitettavasti ehditty vielä tehdä, mutta kaikki välineet sitä varten on nyt toteutettavissa. Myös mahdollisuuksia referenssinäytteen valmistamiseksi on tutkittu.

Avainsanat: Opinnäyte, kolloidikiteytys, polystyreeni, fononikiteet, SINIS tunneliliitos

# **Preface**

The work presented in this thesis has been carried out at the Department of Physics and Nanoscience Center at the University of Jyväskylä. All of the fabrication steps were carried out inside the Nanoscience Center cleanroom facilities. I carried out research training (FYSS9470) alongside the Master's thesis project, and it is reported in this thesis. The aim of the research training was to cover as many sample fabrication steps from the beginning as time allowed and further work was continued as Master's thesis project. The research training is covered in sections 3.3-3.6.

First, I would like to thank my supervisor, Professor Ilari Maasilta for giving me an opportunity to work on such interesting topics and also for his guidance and ideas along the project. Moreover, I would like to thank Mr. Zhuoran Geng for all of his practical help with cleanroom equipment and beyond. Cooldowns were carried out by him and he guided me through the measurements, and he also did indium bonding to my samples. He kindly let me use his code to simulate simple theoretical curves presented in sections 4.3 and 4.5 and he performed the actual simulations for spin-split and -polarization effects which are presented in section 4.4. I would also like to thank Mr. Samuli Heiskanen for his help with the equipment and sharing his fabrication knowledge, especially used in evaporation. Thanks to Dr. Kimmo Kinnunen for lending his skills with bonding machine and to him along with Mr. Tarmo Suppula for their efforts in keeping the equipment working and labs in order. My gratitude goes also to current and former group members who have provided me with help and ideas, especially to Mr. Teemu Loippo for interesting fabrication discussions.

Most of all, I am thankful to my family and friends for their encouragement, especially to my parents Tommi and Pauliina Kirjanen and my fiancé Oskari Saarimäki for their support.

Jyväskylä, December 2018

Emmi Kirjanen

# Contents

| Abstract         |                        |         |                                                                     |    |  |  |  |  |  |

|------------------|------------------------|---------|---------------------------------------------------------------------|----|--|--|--|--|--|

| $\mathbf{T}^{i}$ | Tiivistelmä            |         |                                                                     |    |  |  |  |  |  |

| Preface          |                        |         |                                                                     |    |  |  |  |  |  |

| 1                | Introduction           |         |                                                                     |    |  |  |  |  |  |

| 2                | Theoretical background |         |                                                                     |    |  |  |  |  |  |

|                  | 2.1                    | Thern   | nal phononic crystals                                               | 13 |  |  |  |  |  |

|                  |                        | 2.1.1   | Diffusive heat conduction                                           | 13 |  |  |  |  |  |

|                  |                        | 2.1.2   | Ballistic heat conduction                                           | 14 |  |  |  |  |  |

|                  |                        | 2.1.3   | Thermal phonon radiation                                            | 15 |  |  |  |  |  |

|                  |                        | 2.1.4   | Two-dimensional phononic crystals                                   | 15 |  |  |  |  |  |

|                  |                        | 2.1.5   | Three-dimensional phononic crystals                                 | 18 |  |  |  |  |  |

|                  | 2.2                    | SINIS   | thermometry                                                         |    |  |  |  |  |  |

|                  |                        | 2.2.1   | Superconductivity                                                   |    |  |  |  |  |  |

|                  |                        | 2.2.2   | Tunneling between superconductor and normal metal                   |    |  |  |  |  |  |

|                  |                        | 2.2.3   | SINIS junction current                                              |    |  |  |  |  |  |

|                  | 2.3                    |         | dal crystals                                                        |    |  |  |  |  |  |

|                  |                        | 2.3.1   | Self-assembly in colloidal crystallization                          |    |  |  |  |  |  |

|                  |                        | 2.3.2   | Crystallization by single-step vertical deposition                  |    |  |  |  |  |  |

|                  |                        | 2.3.3   | Lithographically assisted self-assembly                             |    |  |  |  |  |  |

|                  |                        | 2.3.4   | Considerations with organic colloid materials                       | 26 |  |  |  |  |  |

| 3                | Fab                    | ricatio | on                                                                  | 29 |  |  |  |  |  |

|                  | 3.1                    | Imagir  | ng and visualization                                                | 29 |  |  |  |  |  |

|                  | 3.2                    | Overv   | iew of the fabrication                                              | 29 |  |  |  |  |  |

|                  | 3.3                    | Prepa   | ration steps                                                        | 30 |  |  |  |  |  |

|                  |                        | 3.3.1   | Cutting of silicon wafer                                            | 30 |  |  |  |  |  |

|                  |                        | 3.3.2   | Cleaning of silicon chips                                           | 32 |  |  |  |  |  |

|                  | 3.4                    | Photo   | resist template                                                     | 32 |  |  |  |  |  |

|                  |                        | 3.4.1   | Mask used in template exposure                                      | 32 |  |  |  |  |  |

|                  |                        | 3.4.2   | Materials and methods for template making                           | 33 |  |  |  |  |  |

|                  |                        | 3.4.3   | Photoresist template results                                        | 33 |  |  |  |  |  |

|                  | 3.5                    | Colloi  | dal crystallization                                                 | 36 |  |  |  |  |  |

|                  |                        | 3.5.1   | Materials and methods for single-step vertical deposition $\ . \ .$ |    |  |  |  |  |  |

|                  |                        | 3.5.2   | Crystallization results                                             | 37 |  |  |  |  |  |

|              | 3.6   | Electron beam irradiation                                        | 41          |

|--------------|-------|------------------------------------------------------------------|-------------|

|              |       | 3.6.1 Preliminary solubility test for crystals                   | 41          |

|              |       | 3.6.2 Crystal solubility results                                 | 42          |

|              |       | 3.6.3 Materials and methods for electron beam irradiation        | 42          |

|              |       | 3.6.4 Electron beam irradiation dose test results                | 44          |

|              | 3.7   | SINIS fabrication                                                | 46          |

|              |       | 3.7.1 Three-dimensional laser lithography                        | 46          |

|              |       | 3.7.2 Evaporation and lift-off                                   | 47          |

|              |       | 3.7.3 Test design with straight wires                            | 48          |

|              |       | 3.7.4 Test deposition with gold                                  | 48          |

|              |       | 3.7.5 SINIS pattern design                                       | 49          |

|              |       | 3.7.6 SINIS two-angle deposition                                 | 51          |

|              |       | 3.7.7 SINIS fabrication results                                  | 52          |

|              | 3.8   | Control sample                                                   | 55          |

|              |       | 3.8.1 Materials and methods for polystyrene thin film            | 55          |

|              |       | 3.8.2 Spin coating results                                       | 56          |

|              |       | 3.8.3 Control sample fabrication                                 | 57          |

| 4            | Mea   | asurements                                                       | 59          |

|              | 4.1   | Attaching sample to the sample stage                             | 59          |

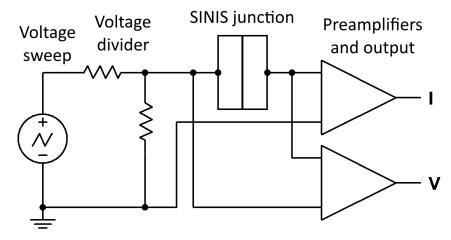

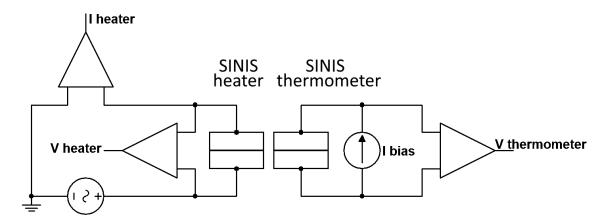

|              | 4.2   | Measurement set-up and scheme                                    | 61          |

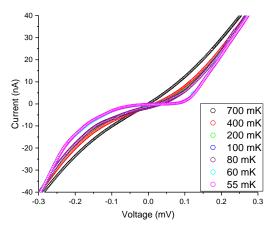

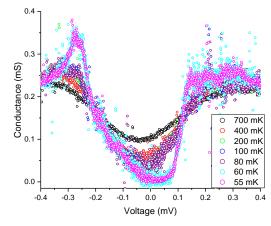

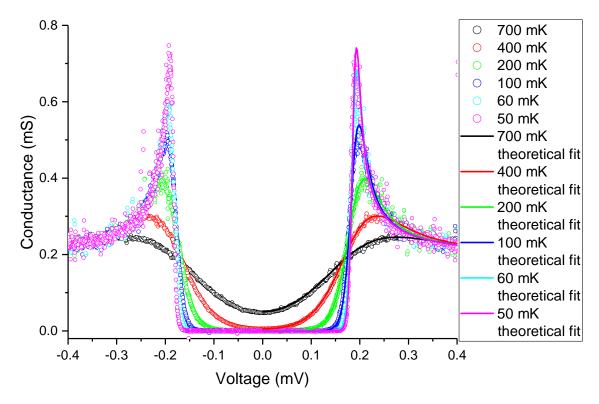

|              | 4.3   | Characterization of single SINIS junction                        | 62          |

|              | 4.4   | Analysis of SINIS junction measurement with spin-splitting and - |             |

|              |       | polarization                                                     | 66          |

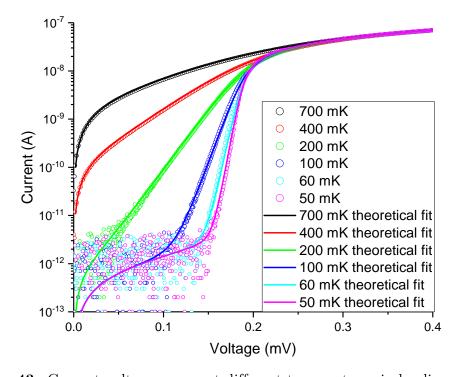

|              | 4.5   | Characterization of single NIS junction                          | 69          |

| 5            | Cor   | nclusions                                                        | 73          |

| ъ            | . C   |                                                                  | <del></del> |

| K            | efere | nces                                                             | <b>7</b> 5  |

| $\mathbf{A}$ |       | pendix                                                           | <b>7</b> 9  |

|              | A.1   | Typical code for Nanoscribe                                      | 79          |

## 1 Introduction

Colloidal crystals have been widely used to make photonic crystals (PtCs). PtCs have a periodic structure with a varying dielectric constant. PtCs will have an effect on how light propagates inside the crystal, which will result in a complex photonic band structure. The band structure describes which wavelengths are able to travel inside the material, in which direction and with which speed. [1] Phononic crystals (PnCs) are analogous to PtCs, except that mechanical vibrations are modified instead of electromagnetic waves. In PnCs, the periodic structure has alternating densities of materials, as the name suggests, phonons are the quantum mechanical quantity for vibrations just like photons are for light. Likewise, PnCs can be fabricated from colloidal crystals. [2]

PnCs can be used to control how vibrations, and so also heat carried by them, are transmitted. They can block certain wavelengths completely or in certain directions. These restricted spectral regions are called band gaps. PnCs can hinder or enhance propagation by the modifications to the band structure. With these properties, it is possible to use PnCs for insulation or to make good thermal contact in the case of thermal transport. There are also some other novel ideas, such as guiding or focusing vibrations. [3] The properties of PnCs can be radically changed or fine tuned by altering the geometry, the material, the filling factor or the lattice constant. The effects of different structures have been studied a lot, both experimentally and computationally. [2, 4, 5]

While there has been a lot of focus on two-dimensional (2D) PnCs [6] and their possibilities, three-dimensional (3D) PnCs can also be used in similar ways. However, fabrication of 3D PnCs can sometimes prove to be challenging. One of the problems is of course how to fabricate good quality 3D periodic structure. Self-assembled colloidal crystals is a promising solution to that. Nevertheless, the optimization of the fabrication process can be crucial. In addition, with the usual self-assembly techniques, the crystal is usually deposited on top of the whole surface and it produces multiple domains instead of one single crystal. This can cause problems for measurements where usually single domain crystals are wanted. [7]

2D PnCs have been fabricated from different types of membranes by patterning them with hole arrays. However, whereas 2D PnCs can have a flat surface by default, the top of 3D PnC is rough when it is formed by colloidal crystallization. This can cause problems if some sort of fabrication on top of the structure is necessary for measurements. One such option is a nanofabricated heater-thermometer pair that can be used to measure the thermal conductance locally. [4] Restricting the place and

size of the crystal is also important for wire fabrication. In addition, the stability of the crystals is of concern, especially when using organic materials which can be vulnerable to many chemicals. Electron beam irradiation seems to be suitable to control polystyrene (PS) durability [8], which is also the material that is used in this study.

The aim of this study is first to reproduce the previous results by Tian et al. [8], then to optimize sample fabrication and continue it further to produce final devices for thermal transport studies. Before this work, 3D colloidal crystals have been fabricated from a PS microsphere suspension with a single-step vertical deposition. It has been possible to influence the crystal size and position with pre-crystallization lithographic methods, with either an etched silicon trough or with a patterned photoresist. From these two, photoresist seemed more promising so I continued with it. I tried the more straightforward method of using simple UV patterned resists instead of 3D lithography. In addition, as PS is vulnerable to harsh chemicals used in post-crystallization fabrication, I made sure what type of treatment is necessary. Afterward, I deposited metallic wiring in the form of superconductor - insulator normal metal - insulator - superconductor (SINIS) heater-thermometer pairs, similar to Zen et al. [4] in design and materials. Novel combination of 3D lithography and electron beam evaporation was used. I investigated if fabrication is possible directly on top of the crystal, whether the junctions behave according to theory, and whether they are suitable to be used as thermometers. For the finished samples, thermal properties are planned to be measured at sub-Kelvin temperatures. These measurements could then be compared to results from a control sample with a continuous structure, and thus the effect of the 3D PnC could be determined.

# 2 Theoretical background

# 2.1 Thermal phononic crystals

### 2.1.1 Diffusive heat conduction

Thermal conductivity is a property of matter. It describes at which rate heat is transferred in a material. It can be defined as rate of heat flow per area  $(\dot{q} = \dot{Q}/A)$ , given by the thermal conductivity coefficient times the temperature gradient  $(\dot{q} = -\kappa \nabla T)$ , which is the differential form of Fourier's law. The thermal conductivity coefficient can easily be used to describe the properties of matter and it is usually temperature dependent. [9]

Heat is mainly carried by conduction electrons or by phonons in a solid. Phonons are the quantized lattice vibrations. Insulators lack conduction electrons so only phonons can carry heat in them. For most samples and temperatures phonon transport is a diffusive process, where phonons scatter from electrons, phonons or impurities. The kinetic model for thermal conductivity coefficient can then be written as:

$$\kappa = \frac{1}{3} \frac{C}{V_m} v \lambda \,\,\,\,(1)$$

where C is the specific heat,  $V_m$  is molar volume, v is the average velocity of heat carriers, and  $\lambda$  is the mean free path. Mean free path is the average distance that the heat carrier (a phonon in case of insulators) can travel before scattering. Some scattering processes are temperature dependent such as phonon-phonon scattering, while others are not, such as phonon-impurity scattering. The velocity of phonons, which is the velocity of sound for acoustic phonons, is temperature independent at low temperatures. The phononic specific heat can be calculated, and it is known to have  $T^3$  dependence at low temperatures. This way it is possible to write an approximation for the phononic thermal conductivity coefficient:

$$\kappa_{ph} = \frac{1}{3} \frac{C_{ph}}{V_m} v_S \lambda_{ph}(T) \propto T^3 \lambda_{ph}(T) \quad \text{at} \quad T \le \theta_D / 10 ,$$

(2)

where  $\theta_D$  stands for the Debye temperature, which means that the equation is valid for so called intermediate temperatures. For temperatures significantly lower than Debye temperature, the number of exited phonons is small and their wavelength is long, which means that most scattering processes become negligible. Phonons will scatter mostly at crystal boundaries which is a temperature independent process. For perfect crystals  $\kappa_{ph}$  then becomes  $T^3$  dependent. [9]

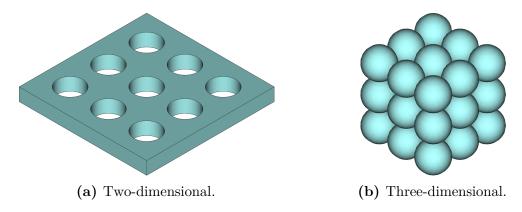

Figure 1. Examples of phononic crystal structures.

### 2.1.2 Ballistic heat conduction

Diffusive scattering leads to incoherence. This means that phonons will lose their phase during scattering. Instead, in coherent scattering the phase of phonons is preserved. Coherent scattering occurs at sample boundaries if the surface is smooth enough compared to the wavelength of the phonon. Coherent scattering combined with periodic structures makes it possible for phonons to interfere with each other either destructively or constructively. Multiple periods are required for the effect to show. The phonon band structure (phonon dispersion relations) is modified by interference, which turns usually diffusive particles to behave as phonon waves. As phonons are vibrations of the lattice, the elastic properties of materials affect the propagation, and thus the phononic band structure. Other determining factors are the shape and the arrangement of the periodic structure (crystal). Crystals that can be used to control phonon propagation are called phononic crystals. [10, 11]

Phononic crystals (PnCs) can be realized in many dimensions, some of which are presented in Figure 1. For example, one-dimensional layered structures, two-dimensional hole (or pillar) patterns on a plate, or three-dimensional such as spheres arranged in lattice can all serve as PnCs. However, in all three cases the periodicity of the PnC affects the possible formation of a band gap. The band gap is a range of frequencies, which do not support propagation inside the PnC. A partial band gap means that selected frequencies are prohibited only to some directions, and a complete band gap means that those frequencies can not propagate at all inside the PnC. Band gaps are mainly formed from Bragg interference which occurs at frequencies around c/a, where c is speed of phonons and a is period of PnC. This means that periodicity of PnC should be chosen according to which frequencies are the area of interest. For example, to control kHz frequencies periodicity in the order of cm is suitable, for GHz order of µm, and for THz order of 10 nm. [11, 12]

Both sound and heat are lattice vibrations which are carried by phonons. The only difference is the frequency range at which they propagate. Sound is carried by low-frequency phonons, in kHz range, and heat is carried by a wide range of higher

frequency phonons, THz range at room temperature. This makes experimental study of coherent thermal conductance challenging because of the fabrication difficulties of such delicate structures. It also gives high requirements for surface smoothness. [10, 11] To make experiments possible, the frequencies of thermal phonons should be made lower. One suggestion is to use an alloy material where there are a lot of high-frequency scatterers. This would restrict propagation of high-frequency phonons, and heat would have to be carried more by lower-frequency phonons. [13] Another solution, which will be the focus of this study, is to perform experiments at low temperatures, below 1 K. Low temperatures will increase the wavelength of the dominant thermal phonons and the main excitations will be in GHz range. [4]

### 2.1.3 Thermal phonon radiation

In order to study phonons, they must be introduced to the sample in controlled manner. At low temperatures there are only very few excited states because of the low thermal energy. In addition, the mean free path is not limited by phonon-phonon interactions. In insulators only phonons are in charge of the thermal conductance. However, thermal phonons can be generated by heating the sample with a metallic thin film. If a metal film is considered to have phonon distribution corresponding to temperature  $T_1$  and it is treated as an isotropic material, the net phonon power emitted by the heater per area at low temperatures (much lower than Debye temperature) and with perfect matching conditions (emissivity = 1) can be written as:

$$\frac{P(T_1, T_0)}{A} = \frac{\pi^2}{120\hbar^3} \left(\frac{1}{c_l^2} + \frac{2}{c_t^2}\right) \cdot k_B^4 \left(T_1^4 - T_0^4\right) , \qquad (3)$$

where  $T_1$  and  $T_0$  are temperatures of heater and insulator,  $\hbar$  is the reduced Planck constant,  $c_l$  and  $c_t$  are the longitudinal and transverse speeds of sound, and  $k_B$  is the Boltzmann constant. This is the phononic equivalent to the Stephan-Boltzmann law for photon thermal radiation. [14]

### 2.1.4 Two-dimensional phononic crystals

In general, two-dimensional (2D) phononic crystals can be realized with either periodic holes (or pillars) in one plane, as presented in Figure 1a. Hole structures are usually made from suspended thin films, as the thickness of the film also affects the phonon band structure. A band gap might even open only for a specific period to thickness ratio. [4] Silicon and its derivatives are common materials for such membranes. In the following, some advancements made with low-temperature 2D PnCs are reviewed.

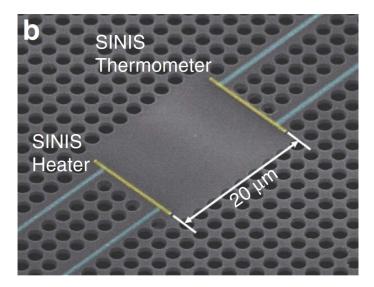

The first report on coherent thermal conductance in 2D PnCs was made by Zen et al. [4]. In that study, silicon nitride membranes were used to make periodic structures with a square lattice array. The chosen periods were 970 nm and 2425 nm with a

**Figure 2.** Fake color SEM image of 2D PnC sample with SINIS tunnel junctions. Yellow color represents copper and blue aluminum. [4]

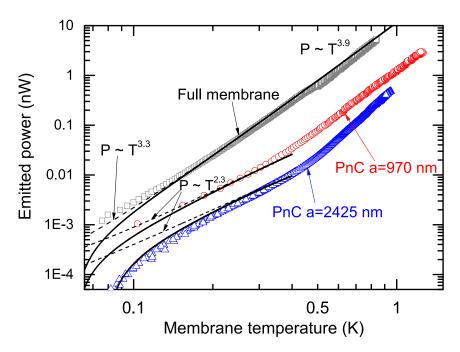

**Figure 3.** The emitted phonon power as a function of temperature for a full membrane and two 2D PnCs with different periods. [4]

membrane thickness of 485 nm. Finite element method (FEM) calculations were utilized to predict phonon dispersion relations. From the calculated band structures it was shown that the smaller period had a complete band gap in the dominant frequency range, and in addition, both periods had much flatter band structures compared to the full membrane, which will also affect thermal conductance. Despite different periodicities, both samples were fabricated with the same filling factor for easier comparison between the PnCs. If the filling factor is the same, and thus the surface to volume ratio, classical or ballistic heat conduction would predict the same values for both samples. However, for the case of the PnCs, the band structures modify the heat conduction and produce coherent changes. Measurements were carried out below 1 K where bulk scattering of phonons is negligible, and where the wavelength of thermal phonons is long. Thermometer-heater pairs of SINIS tunnel junctions were used to heat and measure the temperature locally in the middle of the sample. The principles and applications of SINIS junctions are explained in more detail in section 2.2. The sample with the larger period is presented in Figure 2, and the measurement results in Figure 3. It was found out that both PnC structures had a lower thermal conductance compared to the full membrane by one to two orders of magnitude. Despite the smaller period sample having the band gap in its band structure, the longer period showed a smaller thermal conductance. It can be said that dispersion relations as a whole are more important than band gaps when it comes to thermal conductance. In addition, as the two PnCs with the same filling factor had different thermal conductivities, it was confirmed that it can not be explained by ballistic conduction alone. Instead, the band structure modifications have to be taken into account. That is further confirmed, as the computational calculations for the thermal conductance fit the experiments really well.

Afterwards, silicon nitride membranes have been used for PnCs with longer periodicities. A periodicity of 4 µm was studied [15] with smaller SINIS junctions placed closer together compared to the previous study. Over two orders of magnitude reduction in thermal conductance was achieved compared to a full membrane. PnCs with periodicities of 4  $\mu$ m, 8  $\mu$ m, and 18  $\mu$ m were also fabricated [16, 17] with again a different SINIS geometry and this time also heater/thermometer material. This was done in order to use the same heater geometry for all samples with different periodicities, as it was necessary to fit the wiring to all samples despite the holes having different sizes. It was again observed from the measurements that all PnCs had a lower thermal conductance compared to a full membrane. Interestingly, the middle periodicity, 8 µm, had the lowest value instead of the longest periodicity. This is believed to be due to increase in diffusive scattering with increasing period. That is because with increasing period the sample dimensions become large, comparable to the mean free path, and diffusive scattering could increase thermal conductance by starting to increase the group velocity. All of these silicon nitride membrane PnCs were measured at sub-Kelvin temperatures.

Later, coherent thermal effects of 2D PnCs have been experimented with different set-up by using thin silicon membranes as samples at 4 K temperatures and by

carrying measurements with an optical system. Effects of different geometries have been studied by Anufriev et al. [18], where they fabricated hole-arrays with hexagonal, square and honeycomb lattices. All geometries and periodicities showed lower thermal conductance compared to a full membrane. More than the lattice type, the period and the neck size seemed to have bigger effect on conductance. Measurements were also carried out at high temperature, 300 K, for comparison. Coherent thermal scattering was not demonstrated at such high temperatures where frequency of thermal carriers is much higher. Another interesting way to prove the coherent modifications in a periodic structure was used by Maire et al. [19] where they used a similar type of samples and measurement scheme as in [18]. They fabricated samples with a square lattice but also introduced disorder to samples by randomly shifting the positions of the holes. With increasing disorder the thermal conductance was found to be increasing, reaching a maximum value near 5 % disorder. By repeating the measurement at room temperature, the same effect was not present, and all PnCs had the same thermal conductivity despite the amount of disorder. That was interpreted to demonstrate that the coherent effects were present only at temperatures lower than 10 K. Similar conclusions were also reached by Lee et al. [20]

### 2.1.5 Three-dimensional phononic crystals

Three-dimensional (3D) thermal PnCs have proven to be more challenging to fabricate compared to lower dimensional PnCs. FEM modeling of simple cubic 3D polystyrene PnCs [21] has predicted modifications to band structures and even band gaps, and so 3D PnCs are expected to have big effects on thermal conductance. Visual presentation of such a crystal is in Figure 1b.

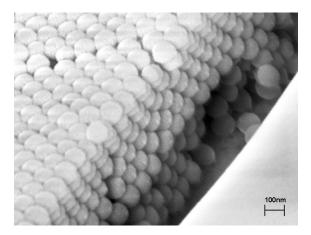

One attempt at a fabrication of a low temperature 3D PnC was made by Savytskyi [22]. He utilized the single-step vertical deposition method, which is explained in section 2.3.2. It was used to make close packed arrays of colloidal crystals formed from silicon dioxide microspheres. However, such crystal is very challenging for further fabrication steps. The surface is rough, and because of that, multiple coating materials and methods were attempted to make it smooth enough. There was also problems with the crystal breaking off during lift-off after metal deposition. Eventually, junction fabrication was made possible with a SU-8 negative photoresist coating between the crystal and the metal. Evaporated metal wires were long enough to travel from a crystal to clean silicon area where bonding to sample stage could be made. This was done because the crystal could still break easily in such a process. Thermal conductance was measured at sub-Kelvin temperatures with SINIS junction pair, and the power of the emitted heat was found to have  $T^{4.15}$  dependence. However, no control sample was made so result could not be compared.

Meanwhile, advances have also been made with polystyrene (PS) microsphere colloidal crystals, by starting with the characterization of crystals formed by single-step vertical deposition [7] and followed by solving problems such as the weak nature of polymers

and roughness of the surface, resulting in successful integration of metallic wiring on top of crystals [8]. However, only simple wires were fabricated on top of crystals, and such samples can not be used for thermal transport measurements. A SINIS pair needs to be on top of a crystal, and in addition, the placement of bonding pads needs to be taken into account. Bonding directly on top of a crystal is most likely impossible with ultrasonic bonding techniques. Instead, positioning of the crystal must be controlled in a way that allows bonding outside of the crystal surface. The ways to control crystal position and size are explained in more detail in section 2.3.3. These challenges need to be addressed before measurements are possible. So far only one microsphere size has been used, with diameter 260 nm, but others are also possible.

# 2.2 SINIS thermometry

### 2.2.1 Superconductivity

Superconductivity is a property possessed by some elements and compounds. Characteristic properties of superconductors are the occurrence of perfect conductivity and perfect diamagnetism when the superconductor is cooled below its critical temperature,  $T_c$ . The critical temperature depends on the material. For example, for aluminum it is as low as  $T_c \approx 1.2$  K. When wires are made from material which is in superconductive state, current can be transferred without losses. According to the Bardeen–Cooper–Schrieffer (BCS) theory, superconductivity is attributed to formation of Cooper pairs. Cooper pairs are formed from two bound electrons. These electrons have a lower energy than unpaired electrons. The formation of pairs causes an energy gap between the ground state and the excited states in superconductor. The gap is centered at the Fermi energy. The gap width is usually denoted with  $\Delta$ , and a minimum energy of  $2\Delta$  is required to break a pair. Energies inside the gap are forbidden. [23]

### 2.2.2 Tunneling between superconductor and normal metal

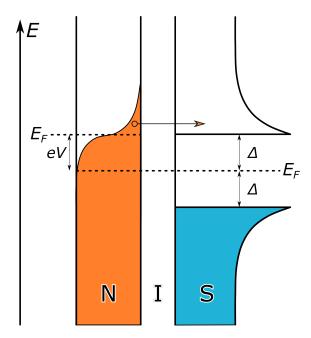

One way to study superconductivity is to observe the tunneling to or from a superconductor. Tunneling is a quantum mechanical effect where electron is transferred from one metal to another through a barrier, which can be a thin insulating layer. This can be achieved by a small potential difference between metals or by thermal excitations. In the case of two normal metals with an insulator between them, the tunneling current is linear as a function of voltage across the junction. The effect of temperature is negligible as the electron distribution is similar on both sides of the insulator. However, if one of them is in the superconductive state, the current-voltage characteristics become highly non-linear. This is due to the energy gap in the superconductor which restricts the current at low voltages. The density of

Figure 4. Energy diagram for a normal metal - insulator - superconductor (NIS) junction at finite temperature. Colored areas represent occupied states and white areas unoccupied states. V is the biasing of the junction.

states is also different compared to a normal metal, and the tunneling current-voltage characteristics are also temperature dependent. At absolute zero, the gap in the superconductor would block all current for voltages smaller than  $|\Delta/e|$ . The energies would all be inside the gap and at such forbidden. However, at higher temperatures there are some thermal excitations which can allow current to flow through even with sub-gap voltages. Depending on the temperature, there are different amount of thermal excitations. This makes tunneling current highly dependent on temperature with small voltages. [24]

This is further illustrated in Figure 4 where a NIS junction is presented in the form of an energy diagram. In the figure, the junction is biased with voltage V which lifts the energy of occupied states in normal metal higher allowing those electrons with high enough energy to tunnel to the unoccupied states in the superconductor.

### 2.2.3 SINIS junction current

In practice, NIS junctions can easily be fabricated in series forming symmetrical SINIS junctions, where there is a normal metal island between two superconductors separated by a thin insulating layer. An example is presented in Figure 2 where there is pair of SINIS junctions facing each other. SINIS junction behaves in a similar way as a single NIS junction with half of the applied voltage. The tunneling current can

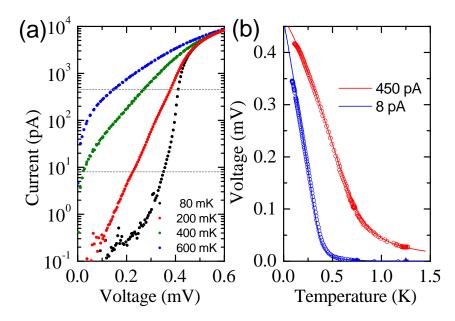

**Figure 5.** An example of SINIS junction thermometer characteristics. On the left side there are current-voltage curves at different bath temperatures, and on the right side there are voltage-temperature calibration curves for two different bias currents. [4]

be written as:

$$I(V) = \frac{1}{eR_T} \int_{-\infty}^{\infty} n_S(E, T_S) \left[ f_N(E - eV/2, T_N) - f_N(E + eV/2, T_N) \right] dE , \qquad (4)$$

where e is elementary charge,  $R_T$  is the total tunneling resistance,  $n_S$  is density of states (DOS) of the superconductor, and  $f_N$  is the Fermi function which describes electron distribution in normal metal. Both  $n_S$  and  $f_N$  are temperature dependent, as  $T_S$  is the superconductor temperature and  $T_N$  is the normal metal temperature. V is the voltage across the whole junction pair. According to the BCS theory, the simplest model for the superconductor DOS can be described by:

$$n_S(E, T_S) = \begin{cases} \frac{|E|}{\sqrt{E^2 - \Delta(T_S)^2}} & \text{when } |E| > \Delta\\ 0 & \text{when } |E| < \Delta \end{cases}, \tag{5}$$

which assumes that there are no states inside the gap. [4, 23] However, non-idealities can cause a small current even inside the gap, and this is present in all measurements. The non-ideal DOS can be expressed as:

$$n_S(E, T_S) = \left| \operatorname{Re} \left\{ \frac{E + i\Gamma}{\sqrt{(E + i\Gamma)^2 - \Delta(T_S)^2}} \right\} \right| , \qquad (6)$$

where  $\Gamma$  is the Dynes parameter. [4, 25]

The current across the SINIS junction given by equation (4) depends on voltage and temperature. If such junction is biased with constant current, the voltage will

depend only on temperature as the current is fixed. It is also important to note that equation (4) depends strongly only on the temperature of the normal metal, and not of the superconductor. The temperature dependent part of superconductor DOS in equation (6) is the gap size  $\Delta$  which is essentially constant at temperatures that are much smaller than critical temperature  $T_c$ . This makes SINIS junctions excellent local thermometers, as ideally only the temperature of the small normal metal island affects the reading. Nevertheless, the temperature of the superconductor plays also a critical role when SINIS junctions are used as a thermometers. The  $T_c$  of the chosen superconductor limits the temperature range where it can be used, because above  $T_c$  the superconductor turns back into a normal metal. In the case of aluminum, it gives an upper limit of around 1 K. [4, 23]

An example of SINIS characteristics is presented in Figure 5. As it can be seen, the shape of the current-voltage curves is greatly affected by temperature at which they are measured. All parameters that are relevant to using SINIS junction as a thermometer can be self-consistently derived from the current-voltage curves. In thermometry measurements, the junction is typically biased with constant current which can be appropriately chosen from the current-voltage characteristics to cover the temperature range of interest. On the left side of Figure 5, the chosen current values are indicated with dotted lines. Multiple current values can be chosen to gain optimal sensitivity at high and at low temperatures. SINIS junction thermometers can be calibrated as presented on the right side of Figure 5, where the voltage across the junction was measured with a constant current bias, and the temperature was measured with a calibrated RuO (ruthenium oxide) thermometer. This is done to correct possible errors. After calibration, a SINIS junction can be used as a local thermometer. [4]

# 2.3 Colloidal crystals

### 2.3.1 Self-assembly in colloidal crystallization

Colloidal crystals are ordered arrays of colloidal spheres. They are typically formed from silica or polymer microspheres from a suspended solution by self-assembly. Highly uniform polymer microspheres can be produced by emulsion polymerization. They can be suspended either in water or some organic solvent, as long as they are insoluble to that solvent. [26] In this study, polystyrene microspheres are suspended in water.

Self-assembly is a bottom-up method which means that crystals are formed from smaller pieces that are independently stacked over each other. Most of the traditional lithographic methods are so called top-down methods. In top-down methods, a bigger piece is modified from outside into a wanted shape, such as how resist is modified by UV light or electron beam. However, self-assembly makes it possible to have small feature size and long range order relatively easily. [27]

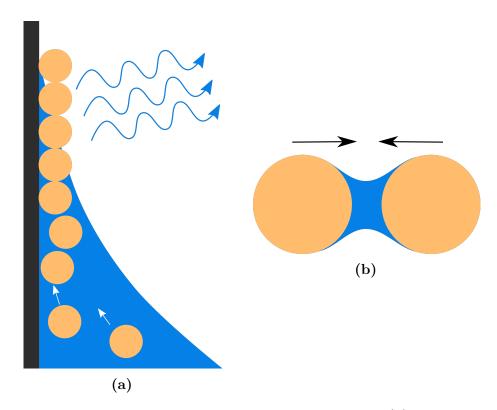

**Figure 6.** Simplified images related to vertical deposition. (a) Solvent flows to the substrate interface where it evaporates (blue arrows), and colloidal spheres move with the flow (white arrows). (b) Capillary neck formation between two colloidal spheres where solvent has been partially evaporated. Arrows indicate direction of attractive forces.

Colloidal crystals formed by self-assembly usually produce close packed geometries such as face-centered cubic (fcc) and hexagonal close packing (hcp), but other geometries are also possible. Colloidal crystallization is entropy-driven process, and there are multiple methods to initiate self-assembly of these colloids. One traditional method is to use gravitational sedimentation, where colloids slowly gather at the bottom of a container and form a crystal. However, the process is really slow and can take months. In addition, there is little control over morphology of the formed crystal and over the number of layers. Samples are usually also polycrystalline. Other possible methods include methods such as utilizing repulsive electrostatic forces, or growing crystals under physical confinement. [1, 26]

### 2.3.2 Crystallization by single-step vertical deposition

The effects of capillary forces and how colloids can gather at interfaces have been studied as well. In one set-up, colloids are laying on a horizontal surface, and the solvent is evaporated. When colloids are partially visible, they start gathering together and form a crystalline layer. This is explained to happen because of

Figure 7. Shape of the meniscus when water is in contact with hydrophilic surface (left) and hydrophobic surface (right).

capillary necks (Figure 6b) that form between spheres and pull them together during drying. [28] Capillary forces have also been utilized in vertical crystal growth where substrate is partially immersed in colloidal suspension perpendicular to the suspension surface. First, colloids flow to the meniscus by the solvent flux, as the solvent evaporates fastest at the contact line at the substrate-solvent-air interface. Then, at the interface, colloids form capillary necks with the substrate surface and with each other, and the crystal is formed. If the movement speed of the contact line is the same as the formation speed of the crystalline layer, a monolayer crystal is formed continuously, as the contact line moves downwards. [29] This is demonstrated in Figure 6a.

Vertical deposition can also be used to form multilayer crystals with same principles. Like in the monolayer formation, colloids gather to the meniscus by the solvent-flux, and are then pulled together by capillary forces. The already formed crystal acts as a filter for upcoming colloids. [30] The two most important and most easily varied factors in multilayer crystal formation are the movement speed of the meniscus and the concentration of the colloidal suspension. The slower the movement of the contact line, the more there is time for colloids to gather to the crystallization area. Likewise, the higher the concentration, the more there are colloids that go with the flow. [1, 31, 32]

There are different approaches to how to control the movement of the contact line. One way is to simply evaporate the solvent. [1] This can be further controlled by such things as humidity and temperature. Evaporation can also be countered by adding more solvent to the suspension at a constant rate. This way even slower speeds can be achieved. [33] However, by simple evaporation, the concentration of the suspension might not stay constant during the deposition process. It causes uneven crystal formation over the substrate by forming distinguishable regions. [34] This can be avoided by lifting the substrate from the suspension with a constant speed which is faster than the evaporation process. Thus the concentration will stay

constant during the whole crystal formation. The lifting speed can easily be varied with right equipment, and the thickness of the crystal can therefore be tuned. [1, 32]

In vertical deposition, the shape of meniscus plays an important role. It determines how colloids travel to the contact line and how much time they have to rearrange. The most important factor seems to be the substrate wetting as presented in Figure 7. The substrate must be hydrophilic for deposition to happen, if water is used in the colloidal suspension. Otherwise, the meniscus is shaped in such a way that colloids can not attach to the surface. The easiest way to alter the wetting of the substrate is to coat it with a hyrdophilic material, but other treatments are also possible. [26] The shape of the meniscus can also be altered by tilting the substrate compared to the suspension surface [35], or with topographical changes in the substrate [36].

In addition to the crystal thickness, the crystal quality is also of great interest. Vertical deposition is reported to produce large, uniform crystals. However, all sorts of defects can be found on colloidal crystals, such as dislocations, changes in crystalline structure and cracks. In vertical deposition, cracks are mainly produced during the drying process. The orientation of crystallites separated by a crack was found to be same, which means that the crack is formed after the crystallization. [34] On the other hand, the size distribution of colloidal particles seems to be important for long range ordering of the crystals. For microspheres with a wide size distribution, the crystalline order resembled amorphous instead of a close packed structure. [31]

Characterization of crystals show that domains separated by cracks are longer in the vertical direction, parallel to the growing direction. In addition, thicker crystals are found to produce larger domains. [31, 37] However, domain sizes are not uniform in one sample. Instead there is a lot of variation in the domain size. [7] Because of this, it can be challenging to make samples with appropriately sized crystals at wanted positions. In addition, thicker crystals can have especially bad adhesion with the substrate, which can cause flaking off or detachment from the surface during further fabrication steps. [8, 34]

### 2.3.3 Lithographically assisted self-assembly

Crystal growth can be modified by using a non-uniform substrate. The changes in the substrate surface affect the shape of the meniscus and also how colloids are attached to the substrate surface. For charged particles, charged regions on the substrate can affect the growth. For neutral particles, changes in surface wettability will affect the shape of the meniscus. As mentioned in the previous section, crystal growth will favor wettable surfaces over hydrophobic. Thus hydrophobic and hydrophilic areas can be patterned for example by depositing a thin layer of different materials. [30]

In addition to chemical or electrical properties of the substrate surface, topographical patterns can also affect crystal growth. Topographical pattern can be made with the same or a different material compared to the substrate. One solution is to etch troughs or pits into the substrate. The meniscus shape is different for etched

and non-etched parts, which can result in favored crystal formation at the deeper parts. [36] This can be further encouraged by depositing more hydrophilic material to the bottom of the etched containers. With an appropriately sized container, it is possible to enhance also the crystal domain size compared to a plain substrate with the same treatment. [7] However, with etched pits made from silicon and crystals made from colloidal polymers, it seems to be common for cracks to form between the container and the crystal. [7, 36] This can be problematic if a continuous structure is wanted to be fabricated from substrate surface to the crystal.

The shape of the assisting pattern also affects the resulting crystal. In the case of templated growth with a chemical pattern, the thickest crystal is formed in the middle of a hydrophilic area. In addition, lines parallel to the growing direction formed nice crystals, while perpendicular stripes were partially unfilled. This is because with parallel lines the meniscus shape is constant, and the crystal can form continuously. On the other hand, with alternating hydrophobic and hydrophilic stripes perpendicular to the growth direction, the meniscus has to flip between different types of surfaces. Also, if the patterned features are too narrow, the meniscus cannot adjust, and no crystal is grown on top of the hydrophilic area, or it is grown on top of the hydrophobic area. [30] In topographical assistance, it is possible to trap a single domain inside one pit, if it is made small enough. [7] However, the shape of a pit does not seem to affect the crack formation at the edge of the crystal. [36]

A promising solution to prevent crack formation is to use polymers to make the confining structure instead of etching. In the work by Tian et al. [8], crystal growth was controlled with a square-shaped container made from a resist. It was found out that while some crack formation was present, crystal edges were nicely in contact with the container.

### 2.3.4 Considerations with organic colloid materials

Polymer spheres, particularly polystyrene (PS) is a common material for colloidal particles used in crystallization. However, one problem with such materials is that their structure can be easily destroyed by heat or strong chemicals. This means that PS must be made more durable for it to withstand additional fabrication steps. One commercially widely used method with plastics and rubbers is to introduce cross-linking by ionizing radiation. It is a method that does not require any chemicals, and is usable for many different polymers with different chemical structures. It can also be used in addition to other cross-linking methods just to give extra strength to the material. Usually radiated materials maintain their shape better, are stronger and even have increased chemical resistance. There are many types of radiation that can be used to initiate the cross-linking, electron beam is one among them. [38]

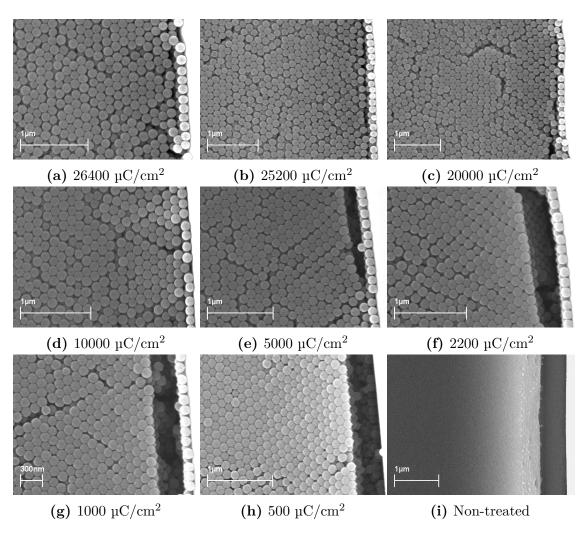

In the work by Tian et al. [8], electron beam irradiation was used to control solubility of thin PS crystals to acetone. It was shown that with just high enough radiation

dose, PS spheres could survive immersion to acetone instead of being completely destroyed. This happened for doses between 60  $\mu C/cm^2$  and 170  $\mu C/cm^2$ . Under doses of 2300  $\mu C/cm^2$ , the solubility was highly tunable. Depending on the dose, the PS spheres would merge more or less together during acetone immersion. With higher doses than that, thin crystals would retain their shape. This is especially interesting, as FEM computational studies [21] have shown, that the contact area between spheres in crystalline lattice can modify the phonon band structure. With a simple cubic (SC) lattice, the band gap would narrow and completely disappear by increasing the contact area.

It was also noted by Tian et al. [8] that thicker crystals might easily peel off even after the electron beam irradiation treatment. However, with a confining structure as explained in previous section, crystals can be trapped into a pit in the substrate. With lithographic assistance, even thicker crystals could stick to the substrate.

# 3 Fabrication

In this section all the sample fabrication details are presented. First there is an overview of the whole process and then separate steps are presented in chronological order. The research training is covered in sections 3.3-3.6.

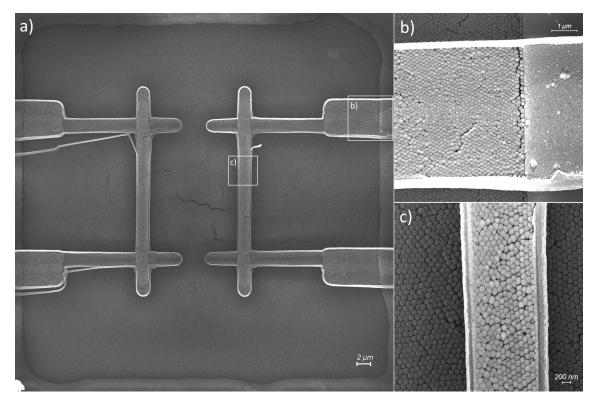

# 3.1 Imaging and visualization

Optical images were taken with an Olympus BX51M optical microscope and a Q Imaging MicroPublisher 5.0 RTV camera. Scanning electron microscope (SEM) images were taken with a Raith eLine scanning electron microscope. It was controlled with the eline and smartSEM software. Both the usual flat and tilted sample stages were used. An aperture size of 30 µm and an acceleration voltage of 10 kV were used. Samples were sputter coated with gold before taking the SEM images. JEOL JFC-1100 ion sputter was used.

Optical and SEM images were edited with paint.net. Inkscape was used to make diagrams and Origin 2017 was used to plot graphs.

### 3.2 Overview of the fabrication

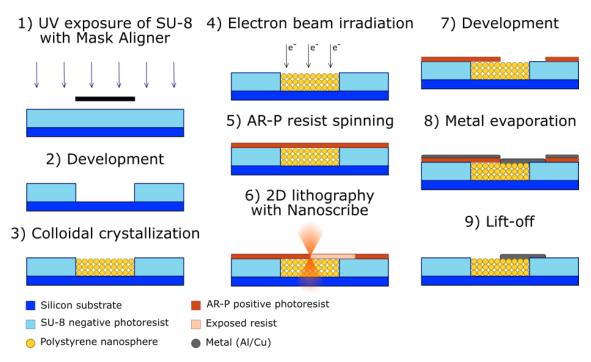

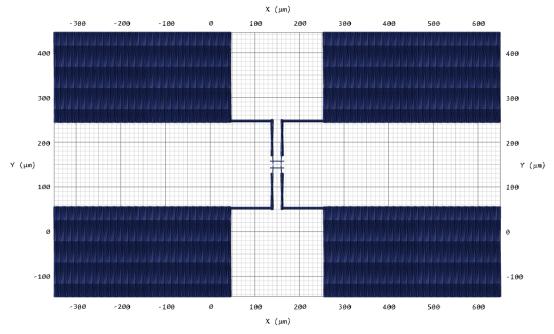

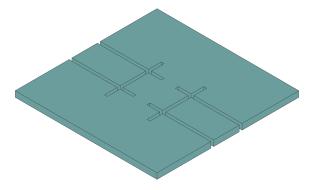

Three-dimensional PnCs were fabricated by combining many previously studied methods. The most important fabrication steps are presented in Figure 8. The numbers in the text represent the numbered steps in the figure. For preparation, the sample is first cut from a silicon wafer and cleaned (described in more detail in section 3.3). After that, 1) the silicon substrate is spin coated with SU-8 negative photoresist, and SU-8 is exposed with UV light by using a mask aligner. Chromium-glass-mask is used to shield  $50 \ \mu m \times 50 \ \mu m$  areas from exposure. 2) The unexposed resist is removed during development. It can be followed by a hard bake to make sure that the resist was fully cross-linked. Steps 1) and 2) are explained in section 3.4.

3) The sample is then "dipped" into a PS microsphere suspension and drawn out slowly using a stepper motor. The method is called single-step vertical deposition. In addition to the control with surface topography, silicon is more hydrophilic than the resist layer which gives control over the crystal growth. The dipping angle is perpendicular to the suspension surface. Step 3) is explained in section 3.5. 4) Crystals are hardened by electron beam irradiation with SEM. Step 4) is covered in section 3.6.

**Figure 8.** Simplified diagram of the fabrication steps after the preparation of the sample.

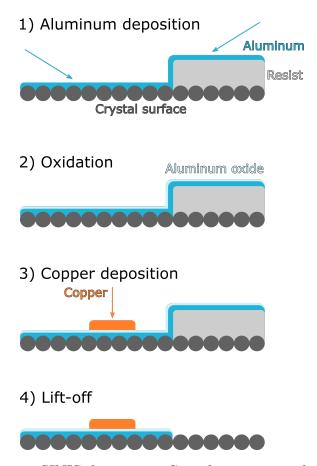

5) A thin layer of AR-P positive photoresist is spin coated on top of the sample. 6) The resist is patterned with Nanoscribe (3D lithography machine) which uses near infrared light and two-photon absorption to expose a chosen pattern. 7) The exposed resist is removed during development. 8) Metal is evaporated on top of the sample, first aluminum, then copper. Two angles are used, and aluminum is oxidized before copper deposition to make tunnel junctions. 9) Lift-off is carried out in hot acetone. It removes the AR-P resist and the deposited metal on top of it, leaving only patterned path left. Steps 5)-9) are covered in section 3.7. After this, the sample is ready to be attached to a sample stage and measurements can be carried out, which is discussed in section 4.

# 3.3 Preparation steps

### 3.3.1 Cutting of silicon wafer

Samples were cut from 525 µm thick silicon wafers using diamond scribe. The sample size was around 8 mm  $\times$  8 mm, as that would be suitable for the sample stage that is used later during measurements. Also longer sample sizes were attempted to be used. This was because longer samples would have been useful for the colloidal crystallization by single-step vertical deposition, as explained in section 3.5. However, getting a uniform resist layer to a 8 mm  $\times$  16 mm sample appeared to be difficult. Positioning such a sample to the spin coater was hard because of the imbalance. In

(a) RIE Oxford instruments (b) Laurell Model WS-(c) Karl-Suss MA45 UV Plasmalab80Plus. 650MZ-23NPPB spin coater. mask aligner.

(d) KLA Tencor P-15 pro-(e) LEO 1430 Scanning elec-(f) Nanoscribe Photonic Profilometer. tron microscope. fessional.

Figure 9. Some of the used equipment.

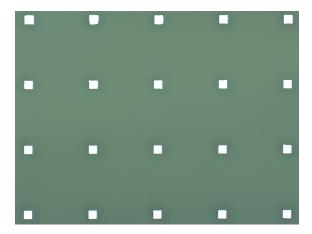

**Figure 10.** Optical micrograph of the chromium mask for photoresist patterning. Light areas are metal, dark areas are glass. One row is left out from the picture. Size of the squares is  $50 \ \mu m \times 50 \ \mu m$ .

addition, the longer chips might not rotate at an appropriate speed.

### 3.3.2 Cleaning of silicon chips

After cutting, the samples were cleaned with hot acetone. The surface was wiped with a cotton stick and the samples were sonicated for 4 minutes in FinnSonic m03 ultrasonic cleaner. Then they were rinsed with isopropanol (IPA) and dried with a nitrogen gas flow. Additional cleaning was done with  $O_2$  plasma by using RIE Oxford instruments Plasmalab80Plus, shown in Figure 9a. The recipe had 50 sccm flow of  $O_2$  at 40 mTorr with power of 200 W for 120 s.

# 3.4 Photoresist template

### 3.4.1 Mask used in template exposure

The mask used in making the photoresist template was a piece of glass patterned with chromium, and it is presented in Figure 10. The pattern had 50  $\mu$ m  $\times$  50  $\mu$ m square areas of approximately 100 nm thick chromium in 5 by 5 array with a 400  $\mu$ m spacing. The fabrication of the mask was was not perfect, as can be seen from the figure. The edges have some surplus deposition. This was most likely caused by a too short lift-off time. Nevertheless, the mask was good enough as the shape of containers was not too crucial for the crystallization. Another mask used at the beginning of this project was similar. The only difference was that there were fever squares (3 by 3) and with smaller spacing (200  $\mu$ m).

### 3.4.2 Materials and methods for template making

The first actual fabrication step was to make the confining structure from negative photoresist. SU-8 2002 (MicroChem) photoresist and Laurell Model WS-650MZ-23NPPB spin coater (Figure 9b) were used. Karl-Suss MA45 UV mask aligner (Figure 9c) was used for the exposure. The UV lamp was left to warm up beforehand, but it still had some fluctuations between different samples. Because of this, the exposure times discussed later are only a guideline. The most reliable way to make the contact between the sample and the mask was to simply place the mask on top of the sample with the metal side down. Immersion in L-ethyl lactate (Fluka Analytical) was used for the development. Developing was stopped with IPA, and samples were dried with nitrogen gas. For finished resist layers, KLA Tencor P-15 profilometer (Figure 9d) was used to measure the resist thicknesses. The system was controlled with Profiler Version 6.41 software. Usually thickness was measured from multiple positions for each sample, and an average was calculated.

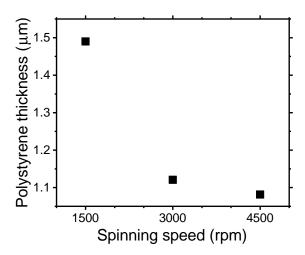

The guidelines provided by the manufacturer [39] were followed. For SU-8 fabrication, the steps are: spin coating on top of a cleaned sample, soft bake to evaporate solvent, exposure with UV light (introduces chemical changes to resist), post exposure bake (actual cross-linking happens), development (unexposed resist is removed), and possible hard bake (makes resist more durable). The varied parameters were the spinning speed (1500-7000 rpm), the exposure time (10-90 s), and the development time (10-120 s). Spinning time was kept as 60 s. The baking times were kept as 1 min for soft bake, and 3 min for post exposure bake, both at 95 °C. The soft bake times were varied for multilayer samples.

Multiple periods are required to see the effects of PnCs. There was thus an interest to fabricate at least 10 layers thick crystals, so the resist layer also needed to be of appropriate thickness. For the spheres with diameter of 140 nm, around 1  $\mu$ m thick resist would be suitable. Thicker layers were also attempted to allow for bigger spheres.

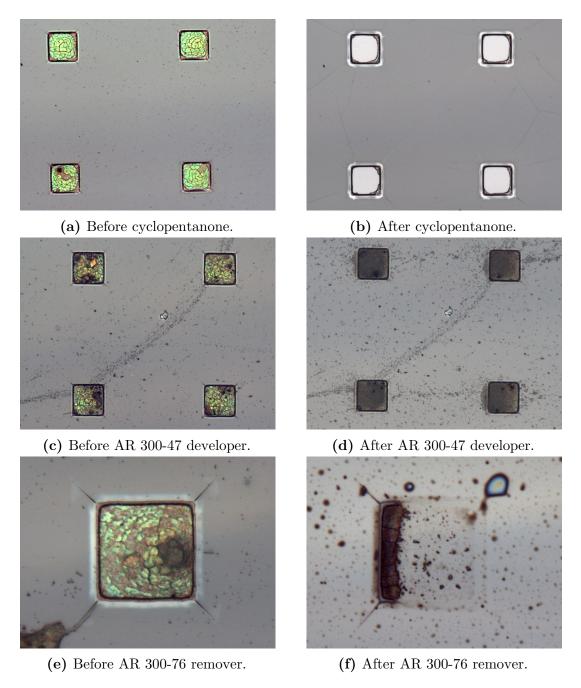

### 3.4.3 Photoresist template results

In the beginning, thicker resist layers were attempted. The aim was to get 10  $\mu$ m thick resist. According to the SU-8 manual [39], one layer of 1500 rpm spin coated SU-8 2002 resist should give roughly 2.5  $\mu$ m thick result. Thicker layers were aimed, but a slower spinning speed would not be a good option because the resist might not spread evenly. Instead, one attempt was to spin multiple layers on one chip with soft bakes between the layers. However, it was found that after the first layer the additional layers gave only a marginal addition to the total thickness. Overall, samples fabricated with a three-layer method had a thickness smaller than 3  $\mu$ m, which is lot less than was expected. Even longer exposure times did not result in thicker resist layers. After the initial layer, the additional spin coated layers gave only  $0.1-0.3~\mu$ m increase to the total thickness. The soft baked SU-8 is probably

Figure 11. Optical microscope images of a sample with extremely cracked SU-8.

still fluid enough that the under layers are affected by additional spinning, and because of that, the increase in thickness is so small. Different underlayer (silicon or SU-8) could also affect the spin coating process. As the multilayer effectivity was so small, it was decided to use only one layer for the rest of the samples.

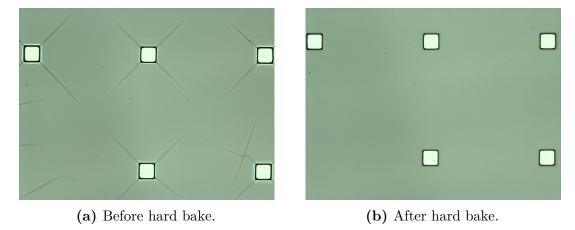

Occasionally, cracks could appear at the corners of patterned squares. One extreme case is shown in Figure 11a. This happened only with thicker resist layers (close to 3 µm) or with longer exposure times (over 45 s). Layers with thickness close to 1 μm did not seem to be as prone to crack formation. In addition, the adhesion of the resist layers seemed to be poor especially for shorter exposure times (under 30 s). Unsufficient sample cleaning before the resist spin coating can also cause poor adhesion. Some of the resist layers even started to peel off after crystallization. That is not good, as SU-8 should be durable enough to withstand later process steps. One possible solution for these problems was hard bake. In the hard bake, the developed sample is reheated. The effect of hard bake is presented in Figure 11. If heating and cool down are done slowly, it will anneal the cracks in resist. It will also make resist more durable. Slow heating and cooling were achieved simply by placing sample on top of a room-temperature hot plate instead of a pre-heated one and, likewise, the sample was kept on the hot plate after switching it off, instead of immediately removing it. As a downside, the hard bake might also affect the shapes of the patterned edges. Corners might become more rounded which is not necessarily wanted. The hard bake did not have notable effect on the thickness for resist layers when the original thickness was a couple of micrometers.

Overall, the geometry of the 8 mm  $\times$  16 mm samples proved to be difficult, especially when thinner layers were attempted. For thinner layers, faster rotation speeds were used during spin coating. Long, narrow samples had to be positioned carefully on top of a sample stage where there is a small area to make the vacuum contact to the sample for keeping the sample in place. However, such a non-traditional shape of the sample affects the spin coating. For the long samples, the SU-8 thickness was highly

Figure 12. SU-8 thickness as a function of spinning speed with three different exposure times.

non-uniform. Oddly shaped contours were visible even to naked eye, and edge beads were really thick. In addition, resist thicknesses were highly non-reproducible with long samples, and they did not seem to follow the usual dependence on spinning speed and exposure time. Faster spinning speed did not necessarily result in a thinner resist. It is speculated that this could be because the vacuum head is relatively small compared to whole sample area, so it could not keep up with higher spinning speeds. The non-uniformity and non-reproducibility problems were solved by making the sample chips smaller and symmetric in both x- and y-directions, the size being 8 mm  $\times$  8 mm.

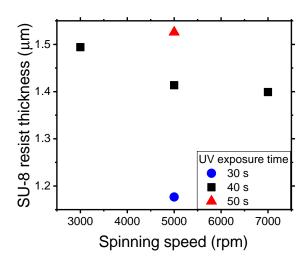

Some resist thickness calibration data is presented in Figure 12. For thinner resist layers spinning speed of 5000 rpm was mostly utilized to get a resist thickness that was close to 1 µm. As seen from the figure, faster spinning speeds did not make it notably thinner. Difference between 5000 and 7000 rpm with an exposure time of 40 s is under 20 nm. It was found, that especially with thicker layers, long exposure times produced deformations to corners of the patterned troughs. Long exposure times also made the final SU-8 layer thicker, as seen in Figure 12. However, with spinning speed of 5000 rpm the thickness seemed to saturate to 1.55 µm, and no thicker layers were produced with even longer exposure times. The exposure times of 30-40 s produced best results as the deformities caused by overexposure appeared with longer exposure times. The development time did not affect the resist thickness by much, but it was also an important factor to sample quality. If the development time was too short, there were impurities that looked like white powder left on top of the sample. Development time of 1 min was found to be suitable.

The final recipe for the SU-8 step was to use 3 droplets of resist on top of 8 mm  $\times$  8 mm sized silicon chip for spin coating with spinning speed of 5000 rpm, soft bake time of 1 min, UV exposure time of 40 s, post exposure bake time of 3 min, and development time of 1 min. Both bakes were done at 95 °C. This resulted in roughly  $1.4 \pm 0.1$  µm

**Figure 13.** Vertical deposition or the so called "dipping" set-up. Sample is attached to a clamp which is connected to a motor. Motor controls the movement of the sample. Sample is first dipped in and then lifted up.

thick resist layer.

It should be noted that SU-8 2002 can be used only to produce resist layers with thicknesses around  $1-3~\mu m$ . For thicker or thinner layers, other concentrations of SU-8 should be used. If thicker samples are attempted in the future with a similar process, there might be a need for some adjustments. Thicker samples were more likely to form cracks. In addition, there should be more consideration to the shape of the side walls with thicker layers. Without filters, thicker layers might not produce vertical side walls, as the absorption of different wavelengths is not uniform through thicker layers [39, 40]. The top will absorb more which can result in an undercut structure or other deformations.

# 3.5 Colloidal crystallization

### 3.5.1 Materials and methods for single-step vertical deposition

Home-made set-up was used for colloidal crystallization by single-step vertical deposition, or the so called "dipping" process. The set-up had humidity and ventilation system connected to a chamber where dipping was carried out. The slowest lifting speed, 0.00675 mm/min, was always used. It was known to produce the best quality [7]. 260 nm and 140 nm diameter PS microsphere suspensions were used. Size distributions were  $\leq 3\%$  CV and  $\leq 6\%$  CV respectively. Both of them

(a) Crystals connected to each other.

(b) Excess and detached crystals.

**Figure 14.** Optical micrographs of crystal deformities with 260 nm diameter microspheres. Square areas are 50  $\mu$ m  $\times$  50  $\mu$ m in both images.

were purchased from Duke Scientific Corporation and original suspensions were 10 % w/w in water. These were diluted with deionized water to get lower concentrations.

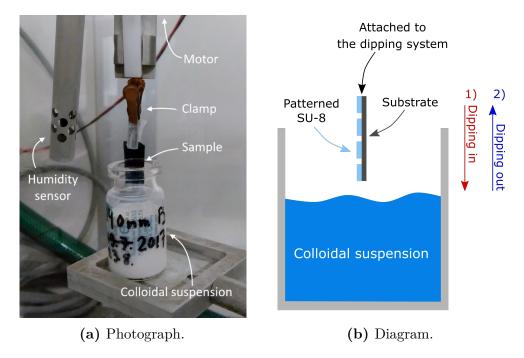

The dipping set-up and process is presented in Figure 13. First, the sample is attached to a clamp at one edge. In the case of smaller sample chips, those were first glued (with Marabu Fixogum) to a piece of plastic that was then attached to the clamp. A bottle with the PS suspension is positioned under the sample. The sample edge is driven closer to the suspension surface manually. After that, the equipment is programmed to quickly dip the sample in. This is done so that the wanted crystal positions are fully immersed in the suspension. Usually, the sample is dipped around 7 mm under the surface. After reaching the lowest position, the sample is slowly lifted up ("dipping out") so that the whole sample rises over the suspension surface. After dipping, the sample is removed from the clamp and then rinsed with deionized water and dried with a nitrogen gas flow.

#### 3.5.2 Crystallization results

The dipping speed was fixed so the other ways to control the crystal thickness were mainly the concentration of the suspension and the humidity of the chamber. The concentration was easily adjusted by diluting the original suspensions with water. However, humidity control was much more difficult. On one side of the dipping chamber, there is humidifier that is directed inside, and on the other side, there is a fan that ventilated excess humidity out. A humidity sensor was used to control a valve between the humidifier and the chamber, but the set-up was still very sensitive to the initial setting on the humidifier. Previous PS microsphere dipping experiments [7] were carried out without an additional humidifier. By those results, 1 % concentration of 260 nm diameter microspheres should be suitable for these samples. The humidifier was used in the beginning. It was also used in the previous dipping experiments with SiO<sub>2</sub> microspheres [22], as it made thinner crystals with

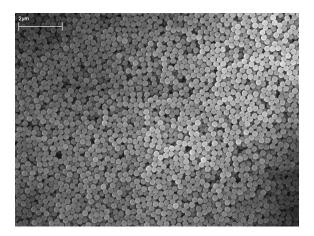

(a) 260 nm diameter microspheres.

(b) 140 nm diameter microspheres.

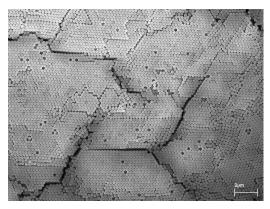

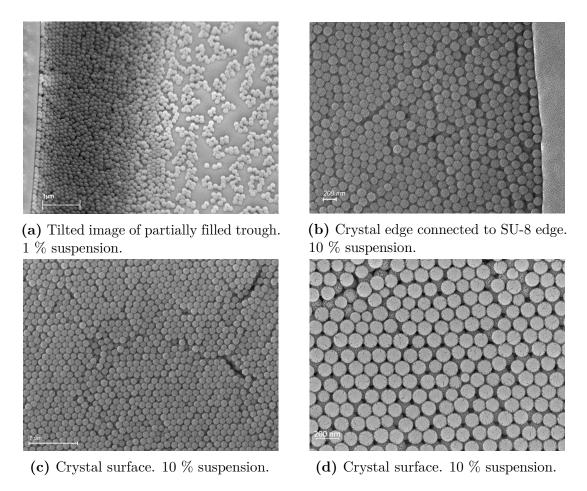

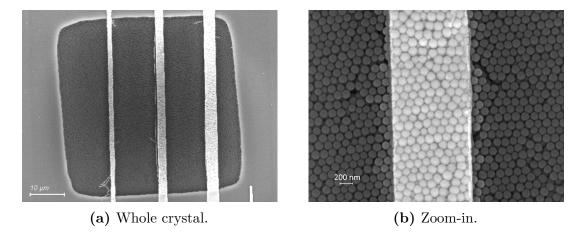

Figure 15. SEM images of typical crystal surfaces. Scale bar is 2 μm long

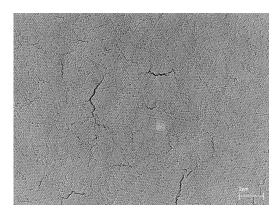

**Figure 16.** Optical microscope images of crystals formed from different concentrations of 140 nm diameter microspheres. All square shaped crystal sites are 50  $\mu$ m  $\times$  50  $\mu$ m.

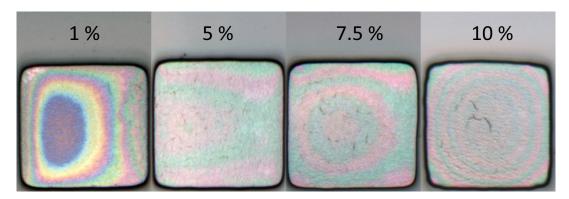

Figure 17. SEM images of crystals formed from 140 nm diameter microspheres.

better quality. However, it was realized that while fan was on, the PS suspension evaporated really fast. Fast evaporation increased the degeneration of the suspension and also made the actual concentration unknown. If the fan was turned off but humidifier left on, the chamber would be so full of water vapor that almost no crystallization could happen. In the end, more reliable results were gained by leaving both the fan and the humidifier off. Relative humidity was then between 33-45 %. It should be noted that some of the suspension would still evaporate during dipping, and later it was also found out that some crystal is also formed at the water-air interface, causing contamination of the suspension. PS is very hydrophobic, which can cause microspheres to attach to each other. Because of this, fresh suspensions are preferred to obtain the best quality.

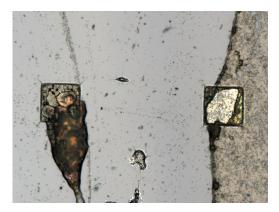

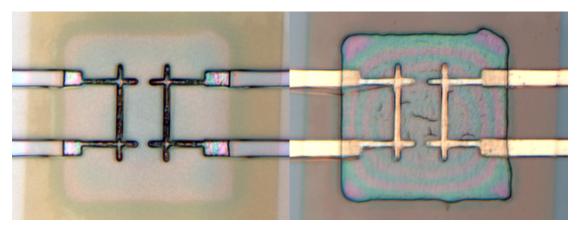

In addition to the unreliability of the humidifier, there were also other challenges. When using the larger microsphere size, 260 nm, the produced crystals could easily grow also on top of the SU-8, despite it being much more hydrophobic than silicon. In addition, the produced crystals might occasionally get exceptionally large and thick and could cover the whole area, where SU-8 was patterned with pits or connect some of them, as seen in Figure 14a. If a pit was completely covered by a large crystal, the whole crystal would most likely detach away when rinsed with water, as shown in Figure 14b. The cause could be that during the dipping, the meniscus might not be able to adjust that well to changes in the surface when pits were close together, as the crystal usually got clumped over all of them. This was mostly countered by making a new mask where pits were further away from each other by growing the spacing between them from 200 µm to 400 µm. However, PS microspheres could still attach to SU-8 and overly large crystals could form. When there were crystals of appropriate thickness, the surface had multiple domains with clear cracks between them, as seen in Figure 15a. Some additional optical microscope images are also presented in Figures 18a, 18c and 18e. Cracks could be in the way of metal deposition, in addition to the unclean surface. It was then decided to try a smaller microsphere size instead, as there might have been some contamination in the suspension that caused the problems.

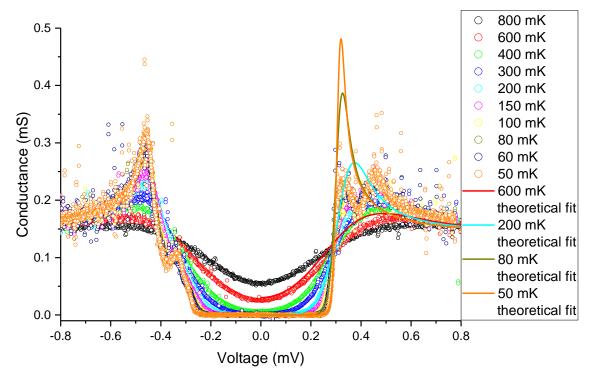

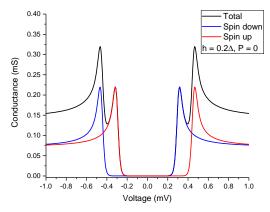

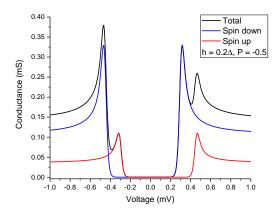

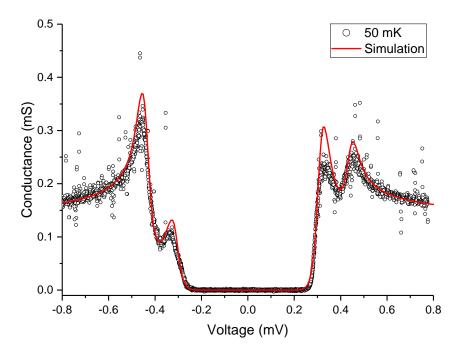

It was clear that with 140 nm diameter microspheres the same concentrations would not work as with the 260 nm spheres. Suspensions with only 1 % concentration could not even cover the bottom of the troughs, as presented in Figure 17a. An optical image of the same crystal is presented in Figure 16 on the far left. Dipping tests were carried out with varying concentrations ranging from 1 % to 10 %. Visual examples of the tests are presented in Figure 16. As can be seen from the images, crystals formed from the smaller sphere size were much less prone to cracking. The amount of cracks would slightly increase by the increase of concentration (and by the increase in thickness) as seen in the figure. The highest concentration would produce thickest crystals, so it was used in further dipping experiments. It was estimated to produce a thickness of around 1 µm by profilometer measurements. Even with the highest concentration, there were no similar problems of huge crystals on top of pits as with the bigger sphere size. Occasionally, a crystal could be deposited even on