## This is an electronic reprint of the original article. This reprint *may differ* from the original in pagination and typographic detail.

Author(s): Andreou, Charalambos M.; Javanainen, Arto; Rominski, Adrian; Virtanen, Ari; Liberali,

Valentino; Calligaro, Cristiano; Prokofiev, Alexander V.; Gerardin, Simone; Bagatin, Marta; Paccagnella, Alessandro; González-Castaño, Diego M.; Gómez, Faustino;

Nahmad, Daniel; Georgiou, Julius

Title: Single Event Transients and Pulse Quenching Effects in Bandgap Reference Topologies

for Space Applications

Year: 2016

Version:

#### Please cite the original version:

Andreou, C. M., Javanainen, A., Rominski, A., Virtanen, A., Liberali, V., Calligaro, C., Prokofiev, A. V., Gerardin, S., Bagatin, M., Paccagnella, A., González-Castaño, D. M., Gómez, F., Nahmad, D., & Georgiou, J. (2016). Single Event Transients and Pulse Quenching Effects in Bandgap Reference Topologies for Space Applications. IEEE Transactions on Nuclear Science, 63(6), 2950-2961. https://doi.org/10.1109/TNS.2016.2611639

All material supplied via JYX is protected by copyright and other intellectual property rights, and duplication or sale of all or part of any of the repository collections is not permitted, except that material may be duplicated by you for your research use or educational purposes in electronic or print form. You must obtain permission for any other use. Electronic or print copies may not be offered, whether for sale or otherwise to anyone who is not an authorised user.

# Single Event Transients and Pulse Quenching Effects in Bandgap Reference Topologies For Space Applications

Charalambos M. Andreou, *Member, IEEE*, Arto Javanainen, *Member, IEEE*, Adrian Rominski, Ari Virtanen, *Member, IEEE*, Valentino Liberali, Cristiano Calligaro, *Member, IEEE*, Alexander V. Prokofiev, Simone Gerardin, Marta Bagatin, Alessandro Paccagnella, Diego M. González-Castaño, Faustino Gómez, *Member, IEEE*, Daniel Nahmad, and Julius Georgiou, *Senior Member, IEEE*

Abstract—An architectural performance comparison of bandgap voltage reference variants, designed in a 0.18  $\mu$ m CMOS process, is performed with respect to single event transients. These are commonly induced in microelectronics in the space radiation environment. Heavy ion tests (Silicon, Krypton, Xenon) are used to explore the analog single-event transients and have revealed pulse quenching mechanisms in analogue circuits. The different topologies are compared, in terms of cross-section, pulse duration and pulse amplitude. The measured results, and the explanations behind the findings, reveal important guidelines for designing analog integrated circuits, which are intended for space applications. The paper includes an analysis on how pulse quenching occurs within the indispensable current mirror, which is used in every analog circuit.

Index Terms—Analog single-event transient (ASET), bandgap voltage reference (BGR), charge sharing, CMOS analog integrated circuits, heavy ion, ionization, pulse quenching, parasitic bipolar effect, radiation effects, radiation hardening by design (RHBD), reference circuits, single-event effects (SEE), single-event transient (SET), space electronics, voltage reference.

#### I. INTRODUCTION

A NALOG single-event transients (ASETs), which belong to the broader category of Single Event Effects (SEEs), are evanescent fluctuations of electrical charges in integrated

- C. M. Andreou is with Cypress Semiconductor, Cork, Ireland and the Department of Electrical and Computer Engineering, University of Cyprus, Nicosia, 1678 Cyprus (e-mail: andreou.m.charalambos@ucy.ac.cy).

- A. Rominski and J. Georgiou are with the Department of Electrical and Computer Engineering, University of Cyprus, Nicosia, 1678 Cyprus (e-mail:julio@ucy.ac.cy).

- A. Javanainen and A. Virtanen are with the Department of Physics, University of Jyvaskyla, FI-40014 Jyvaskyla, Finland (e-mail: arto.javanainen@jyu.fi; ari.j.virtanen@jyu.fi).

- V. Liberali is with the Department of Physics, Università degli Studi di Milano, Italy (e-mail: valentino.liberali@unimi.it).

- C. Calligaro is with RedCat Devices, 20142 Milan, Italy (e-mail: c.calligaro@redcatdevices.it).

- A. V. Prokofiev is with the Department of Physics and Astronomy and The Svedberg Laboratory, Uppsala University, Uppsala, Sweden (e-mail: alexander.prokofiev@physics.uu.se).

- S. Gerardin, M. Bagatin and A. Paccagnella are with the Department of Information Engineering, University of Padova, Padova, Italy (e-mail: simone.gerardin@dei.unipd.it; marta.bagatin@dei.unipd.it; alessandro.paccagnella@dei.unipd.it).

- D. M. González-Castaño and F. Gómez are with the Radiation Physics Laboratory, Universidade de Santiago de Compostela, Santiago de Compostela, Spain (e-mail: diego.gonzalez@usc.es; faustino.gomez@usc.es).

- D. Nahmad is with the R&D Department, Tower Semiconductor, Israel (e-mail: danielna@towersemi.com).

circuits (ICs). They may be observed when high-energy particles (alpha, protons and heavy ions), such as those found in the space environment (trapped particles in the Van Allen belts, solar energetic particles and galactic cosmic rays) [1], collide with analog ICs. When a high-energy particle penetrates the silicon substrate it ionizes the target material along its path. The ionization can occur through coulombic interaction, i.e. through Linear Energy Transfer (LET) or via nuclear reactions e.g. a commonly occurring Boron-10 dopant isotope is struck by a low-energy (thermal) neutron to give a lithium ion and alpha particle. The ionized region is proximal to the ion path, generating a multitude of electron-hole pairs [2]-[6] in the vicinity around the ion track. Built in electric fields or fields created by normal biasing conditions separate the pairs, leaving excess charge after the event. The excess charge injected at a sensitive circuit node can potentially disrupt the reliable functionality of of the circuit, causing instantaneous or permanent failures.

The energy deposited by the impinging ion per unit mass can be expressed by LET. For a unit length of a material it can be expressed in terms of MeV×cm<sup>2</sup>/mg and characterizes the average energy that a charged ion loses as it traverses a unit length of the material (the amount of energy that the ionising particle transfers to the material per unit length per density) [7]-[10]. Observable transients are most likely to occur when the impinging particles are ions with higher LET and hence displace more charge. The effect of the ASETs induced on the desired signals, depend on the sensitivity of the particular analog circuit to the injected charge. The sensitivity is dependent on the circuit architecture, the devices' operating speed and the nominal operating voltage. Furthermore, as the technology nodes scale down, the decreased transistor geometries and thinner gate oxides, reduce the charge required to disrupt normal functionality, thus making the circuits more prone to ASETs. Thus in deep sub-micron technologies [11]-[13] ASETs are of major concern and impose critical issues for the microelectronics reliability, while much ongoing research deals with characterizing the optimum circuit topologies, technology processes, devices and design approaches in order to mitigate ASETs in space applications [14]–[40].

When designing microelectronics for space applications, the constituent circuits and systems have to meet the required specifications of the particular mission, with respect to signal

quality and microelectronics survivability. One of the most essential building blocks in IC design is the voltage reference, which is required for a variety of analogue, mixed-signal and digital circuits [41]–[49] such as flash memories, temperature sensors, amplifiers, DACs, etc. The performance of the voltage reference has a significant impact on the performance of all the subsequent circuits, which depend on the accurate and stable reference voltage/current [50]–[52]. Considering that reference circuits have to be widely used and integrated in modern, deep sub-micron and low-power technologies, the investigation of space radiation induced ASETs, due to heavy ions, are of major importance when designing reference circuits for space electronics [53], [54].

In this work, three bandgap-based reference (BGR) circuit variants have been explored with respect to heavy-ion induced ASETs. The scope of this paper is to reveal important design strategies at the architectural level of these analog circuits, so as to mitigate ASETs. The circuit variants differ with respect to the topology, the use of cascode stages, the supply voltage and the oxide thickness of the utilized transistors. All topologies were implemented using regular radiation-hardening-bydesign (RHBD) layout techniques, such as extended use of guard rings, substrate contacts, increased transistor sizes for hardening against ASETs, whilst edgeless NMOS devices were employed for hardening against total ionization dose (TID) [9], [55], [56]. The integrated circuits were exposed to heavy ions (Si, Kr and Xe) and the resulting ASETs were recorded at the output of each topology independently by using a high-speed oscilloscope. An interesting result was the observation, of pulse quenching phenomena in fabricated analog circuits. We propose useful guidelines for the mitigation of ASET's and enhancement of pulse quenching, that can be used as a mechanism for counteracting the effects at high LETs. These guidelines are applicable to all analogue and mixedsignal circuits.

#### II. CIRCUITS UNDER TEST

ASETs usually originate from particle strikes which traverse reverse-biased pn-junctions or areas with strong electric fields. This is particularly a problem at the transistor's drain terminal, especially with the newer submicron technologies, where the generated plasma of e-h pairs drifts apart because of the high electric fields across the depletion region. The strike-induced extra charge then alters the voltage level of the drain node, as well as subsequent nodes, sometimes even leading to a malfunction of the IC.

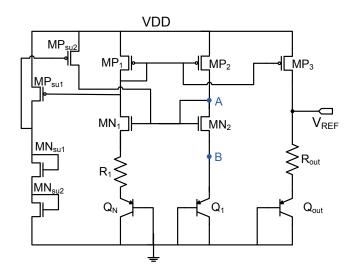

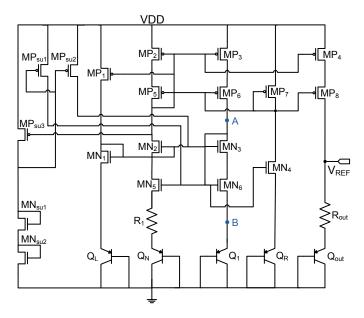

In order to extract the best design strategies for ASET mitigation at the circuit level, the BGR ICs of Fig. 1 and Fig. 2 [57]–[59] were designed and fabricated using TowerJazz Semiconductor's 0.18  $\mu$ m CMOS technology. The circuit in Fig. 1 is based on simple current mirrors (SCM) and was designed in two variations, one with 1. 8V transistors for the corresponding supply voltage of 1.8V and a second one with 3.3 V transistors and its corresponding supply voltage of 3.3 V. The circuit of Fig. 2 is a further variant of the topology of Fig. 1, designed with cascode current mirrors (CCM) and utilizing 3.3 V transistors, targeting a 3.3 V power source. The present

analysis does not take into account radiation effects on the diodes, since these are identical in all circuit implementations that are compared. Standard matching and RHBD techniques such as guard rings and well-substrate contacts are used in all circuits at the layout level so as to improve the immunity to device latchup, radiation induced leakage and ASETs.

Fig. 1. Bandgap voltage reference reference circuit with Simple Current Mirrors (SCM) in two variants: one utilizing 1.8 V transistors and the other utilizing 3.3 V transistors.

Fig. 2. BGR with Cascode Current mirrors (CCM) utilizing 3.3 V transistors.

The SCM and CCM BGR circuits of Fig. 1 and Fig. 2 are based on the principle of summing a PTAT (Proportional to Absolute Temperature) voltage and a CTAT (Complementary to Absolute Temperature) voltage in order to compensate the temperature effects and achieve a temperature independent voltage at the output. Therefore, the voltage across a forward biased pn-junction diode  $(V_{BE(Q_1)})$  is used in order to provide a CTAT voltage. The base-emitter voltage difference  $(\Delta V_{BE(Q_1,Q_N)})$  between two pn-junction diodes with nonequal current densities is used in order to provide a PTAT

voltage via the  $U_T$  (thermal voltage) which increases linearly with temperature. When the two voltages sum together they provide a temperature insensitive voltage. This principle is applied through the topologies of Fig. 1 and Fig. 2 where the current mirrors, that are composed by MP<sub>1</sub>, MP<sub>2</sub>, MN<sub>1</sub> and MN<sub>2</sub> in the case of SCM topology and MP<sub>2</sub>, MP<sub>3</sub>, MP<sub>5</sub>, MP<sub>6</sub>, MN<sub>2</sub>, MN<sub>3</sub>, MN<sub>5</sub>, MN<sub>6</sub> in the case of CCM topology, forces the voltages at nodes B and C to be equal. This creates a  $\Delta V_{BE(Q_1,Q_N)}$  voltage across resistor  $R_1$  which is PTAT and is equal to:

$$\Delta V_{BE(Q_1,Q_N)} = \frac{kT}{q} \ln N \tag{1}$$

where  $V_{BE}$  is the base-emitter voltage T is the absolute temperature, k is the Boltzmann constant  $(1.38 \times 10^{-23} \text{ J/K})$  and q is the electron charge. The output of the reference circuit is the sum of  $V_{BE(Qout)}$  and the voltage drop across the resistor  $R_{out}$  and can be expressed as:

$$V_{REF} = V_{BE(Qout)} + V_{Rout} \tag{2}$$

where  $V_{Rout}$  can be expressed as:

$$V_{Rout} = I_{out} \times R_{out} = I_{R_1} \times R_{out} \implies$$

$$V_{Rout} = \frac{\Delta V_{BE(Q_1, Q_N)}}{R_1} \times R_{out}$$

(3)

Therefore, combining (1), (2) and (3), the reference voltage at the output of the SCM and CCM topologies can be expressed as:

$$V_{REF} = V_{BE(Qout)} + \frac{R_{out}}{R_1} \frac{kT}{q} \ln N \tag{4}$$

where the first term is a CTAT component and the second term is a PTAT component. A low temperature drift can be obtained by properly tuning the ratios of N,  $R_{out}$  and  $R_1$  terms.

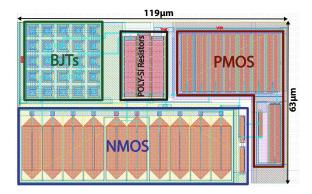

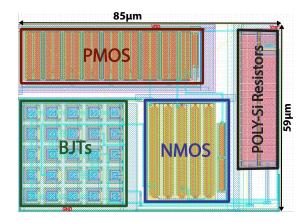

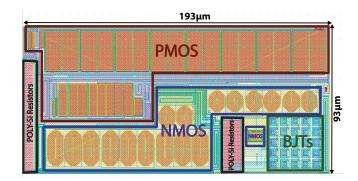

The layout of the SCM BGR topology of Fig. 1 with 1.8 V transistors is shown in Fig. 3 while the one with 3.3 V transistors is shown in Fig. 4. The layout of the CCM BGR topology with 3.3 V transistors of Fig. 2 is shown in Fig. 5. All the NMOS transistors are designed in edgeless shape while extensive guard rings where utilized to enclose all the matched devices groups.

Fig. 3. Bandgap voltage reference reference circuit with Simple Current Mirrors (SCM) utilizing 1.8 V transistors.

The three BGR circuit variants were initially simulated at a schematic level against radiation induced ASETs. The

Fig. 4. Bandgap voltage reference reference circuit with Simple Current Mirrors (SCM) utilizing 3.3 V transistors.

Fig. 5. BGR with Cascode Current mirrors (CCM) utilizing 3.3 V transistors.

simulation was performed with Cadence<sup>®</sup>, by injecting transient current pulses, in order to mimic the local disturbance effects of a heavy ion strike at particular nodes of the circuit, whilst monitoring the circuit output as the disturbance propagates through the whole circuit. The transient current pulses were modelled by utilizing the double exponential law and incorporated into the simulations using Verilog-A. The double exponential current pulse is expressed as [60]–[62]:

$$I(t) = I_0 \times (e^{-t/\tau_f} - e^{-t/\tau_r})$$

(5)

where  $I_0$  is the maximum charge collection current and is equal to  $Q/(\tau_f-\tau_r),\; \tau_r)$  is the current pulse rising time constant and  $\tau_f$ ) is the current pulse falling time constant. For the purpose of the Cadence<sup>®</sup> Verilog-A simulations,  $I_0$ was set at 30  $\mu$ A, while  $\tau_f$  and  $\tau_r$  were set at 7  $\mu$ s and 1  $\mu$ s respectively. The double exponential current pulse was injected at node A and then at node B of the two BGR variants with simple current mirrors (1.8 V and 3.3 V) of Fig. 1 and the corresponding nodes of the BGR with cascode current mirrors of Fig. 2. These circuit nodes were selected since they are those that perturbed the most key elements of a BGR circuit; these are the  $V_{BE}$ , the  $\Delta V_{BE}$  and the current mirror. In addition,  $Q_1$  is approximately twenty times smaller than  $Q_N$  hence for the same charge and current, the perturbation is less due to lower inherent resistance between the collector and the emitter.

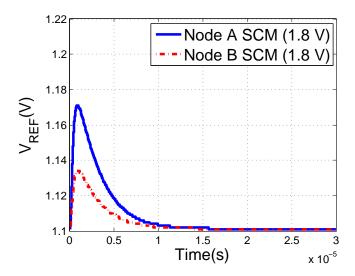

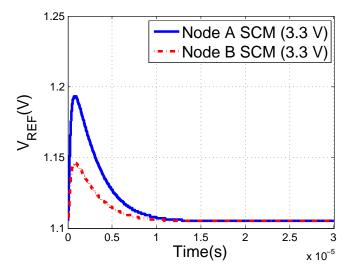

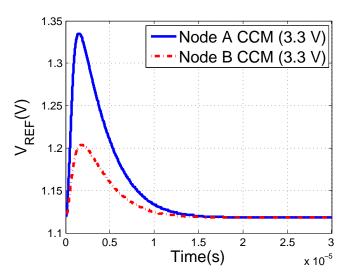

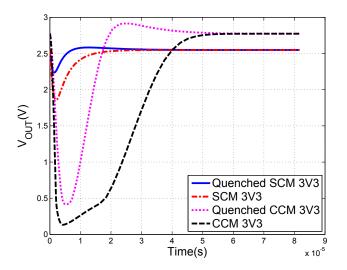

The simulation results for strike-induced charge injection

Fig. 6. Spice simulations of the SCM (simple current mirrors) circuit with 1.8 V transistors by injecting a double exponential current pulse at circuit nodes A and B using a Verilog-A model at the schematic level.

Fig. 7. Spice simulations of the SCM (simple current mirrors) circuit with 3.3 V transistors by injecting a double exponential current pulse at circuit nodes A and B using a Verilog-A model at the schematic level.

at nodes A and B are shown in Fig. 6 for the SCM-1.8V, in Fig. 7 for SCM-3.3V and in Fig. 8 for CCM-3.3V. For both nodes the circuits that show the most resilience, are the circuits with simple current mirrors, which have almost identical results. The circuits containing cascode current mirrors exhibit much stronger transients, both in terms of pulse duration and pulse amplitude. A possible explanation for this, is that the cascode stages increase the resistance to VDD or ground from intermediate nodes, thus impeding the transfer of the additional charge to the small-signal ground terminals and increasing the voltage gain associated with the injected current. Furthermore a slow return to the nominal bias point at a cascoded highimpedance terminal has the effect of allowing the transient to propagate to other nodes, which might have otherwise not have been affected. Thus the two circuit variants of Fig. 1 are more likely to dissipate and hence tolerate excess charge as

Fig. 8. Spice simulations of the CCM (cascode current mirrors) circuit with 3.3 V transistors by injecting a double exponential current pulse at circuit nodes A and B using a Verilog-A model at the schematic level.

opposed to the circuit of Fig. 2.

#### III. EXPERIMENTAL MEASUREMENTS

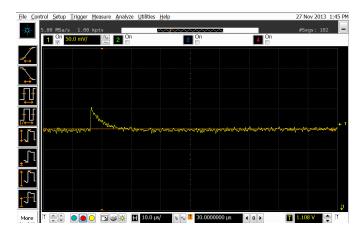

The three variants of this circuit were fabricated in a regular CMOS 0.18  $\mu$ m technology and were tested at RADEF (Radiation Effects Facility) at the University of Jyvaskyla, for ASETs. Heavy ions (Si, Kr and Xe) from RADEF's standard 9.3 MeV/ $\mu m$  cocktail were used in order to provide different LET characteristics, so as to extract the cross-section ( $\sigma$ ) for each circuit design. The circuit irradiations were performed in air with a Kapton foil thickness of 25  $\mu$ m and air thickness of 5 mm. During irradiation, the circuits were biased at nominal supply voltages and the ASETs were recorded using a high sampling-rate oscilloscope (Agilent Technologies DSO9104A 1GHz/20GS/s). The oscilloscope was set to record all the transient segments above a threshold trigger level (12 mV). This level is higher than the reference circuit noise floor and ensures that stray electromagnetic fields at the testing facilities do not trigger the oscilloscope. A typical ASET response with Xe ions, obtained from the circuit SCM - 1.8V of Fig. 1, is shown in Fig. 9. The ASET duration is approximately 10  $\mu s$ and the amplitude is approximately 55mV.

The RADEF's heavy ions cocktail provided Si ions with a LET(Si) of  $\sim$ 6.9 MeV·cm²/mg, Kr ions with a LET(Si) of  $\sim$ 36.1 MeV·cm²/mg and Xe ions with a LET(Si) of  $\sim$ 64.7 MeV·cm²/mg. The charge that will be deposited in the projected material is greater at higher LET.

In order to get a quantitative approach of the charge that each particle can deposit we calculate the  $N_0$  (electron-hole line density) as well as the  $\frac{Q}{L}$  (charge transfer rate per unit length of material penetration) that corresponds to each of the heavy ions that were used in these experiments. The results are presented in Table I where higher LET induces more electron-hole pairs and hence deposits more charge in the material.

In order to evaluate the resilience of the tested circuits when exposed to heavy-ions one has to calculate the cross-section,  $\sigma$ , which is expressed as  $\sigma = N_{ASET'S}/\phi$  (cm<sup>2</sup>)

TABLE I CALCULATED  $N_0$  and  $\frac{Q}{L}$  for the Heavy Ions That are Used in These Experiments

| Heavy Ion                             | $N_0[Si]$ (e-h pair/ $\mu$ m) | $\frac{Q}{L}[Si] (pC/\mu m)$ | $N_0[SiO_2]$ (e-h pair/ $\mu m$ ) | $\frac{Q}{L}[SiO_2] (pC/\mu m)$ |

|---------------------------------------|-------------------------------|------------------------------|-----------------------------------|---------------------------------|

| Si (LET~6.9 MeV·cm <sup>2</sup> /mg)  | $4.45 \times 10^5$            | 0.0712                       | $1.075 \times 10^5$               | 0.0172                          |

| Kr (LET~36.1 MeV·cm <sup>2</sup> /mg) | 2.33×10 <sup>6</sup>          | 0.3728                       | $5.62 \times 10^5$                | 0.09                            |

| Xe (LET~64.7 MeV·cm <sup>2</sup> /mg) | $4.17 \times 10^{6}$          | 0.67                         | 1×10 <sup>6</sup>                 | 0.16                            |

Fig. 9. A measured typical ASET of BGR with Simple Current mirrors (1.8 V transistors), acquired with the oscilloscope during irradiation with Xe ions. The ASET duration is approximately  $10\mu s$  and the ASET amplitude is 55 mV. The scale of the x-axis is is  $10~\mu s$  for every grid time window (scale is shown at the bottom of the image) and of the y-axis is 50 mV for every grid voltage window (scale is shown at the top-left of the image).

where  $N_{ASET'S}$  is the observed number of ASET events and  $\phi$  is the uniform particle fluence (particles/cm²) and depends on the total dose. The time duration was obtained by running a Matlab script on the measured data acquired by the oscilloscope. The script detected the onset and the end of the ASET by using a threshold (1 mV). This was defined to be 10% of the minimum ASET amplitude (10 mV), which was defined to be well above the noise floor of the circuits and any external electrical interferers at the test facility.

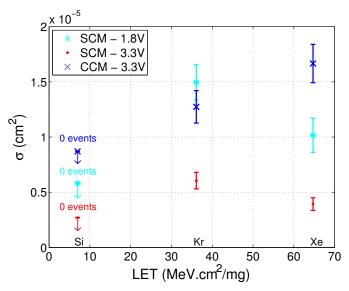

The measured  $\sigma$  for all the BGR circuits variants, including the two versions with simple current mirrors of Fig. 1 with 1.8 V transistors (SCM-1.8V) and 3.3 V transistors (SCM-3.3V) as well as the circuit with cascode current mirrors of Fig. 2 with 3.3 V transistors (CCM-3.3V) are shown in Fig. 10. All the three tested topologies did not exhibit any significant sensitivity to Si ions, (LET $\sim$ 6.9 MeV·cm²/mg) since Si ions were not able to induce detectable transients to any of the circuits.

While using Kr ions (LET $\sim$ 36.1 MeV·cm²/mg), the SCM-1.8V- circuit exhibited a much higher  $\sigma$ , when compared to the SCM-3.3V circuit and slightly higher  $\sigma$  when compared to the CCM-3.3V circuit, as shown in Fig. 10. A possible explanation behind these results is the fact that the SCM-3.3V circuit, which exhibits the lowest  $\sigma$ , has a thicker gate oxide which in circuit terms translates to a lower transconductance per unit area, hence requiring more charge to alter a transistor's steady-state, when compared to the SCM-1.8V circuit. Fur-

Fig. 10. Measured Cross-Section of all bandgap voltage reference circuits variants, including simple current mirrors with 1.8 V transistors (SCM-1.8V), simple current mirrors with 3.3 V transistors (SCM-3.3V) and cascode current mirrors with 3.3 V transistors (CCM-3.3V).

thermore, the SCM-3.3V circuit utilizes fewer cascode stages, which leads to lower impedance to VDD or Ground (smaller time constant) when compared to the CCM-3.3V circuit. The smaller time constant of the ASET decreased the probability that it will propagate to the output of the circuit. In addition, the cascode stages increase the physical distance between the high impedance nodes (which are the most sensitive to charge injection) and the supply rails, hence weakening the electric field that could collect excess charge generated in the substrate. The fact that in Fig. 10, CCM-3.3V shows slightly less  $\sigma$ , when compared to the SCM-1.8V circuit, reveals that gate oxide thickness could be a dominating factor in terms of ASET resilience when compared to the cascode stages.

While using Xe ions (LET~64.7 MeV·cm²/mg) the SCM-3.3V circuit still exhibits the lowest  $\sigma$ , as shown in Fig. 10, for the reasons explained above, though a relatively minor decrease in cross-section, with respect to Kr, is observed. One would expect that the SCM-1.8V would be the worst performer or at least be comparable to the CCM-3.3V, following the trend given by the Kr ions  $\sigma$  result. Paradoxically the  $\sigma$  of the SCM-1.8V drops significantly both in comparison to the CCM-3.3V and in comparison to its Kr  $\sigma$  result, with almost half the LET. This anomaly can only be explained by the pulse quenching phenomenon, that has been observed in other circuits [63].

Fig. 11. Measured number of ASETs Versus ASETs duration for all BGR circuit variants, including simple current mirrors with 1.8 V transistors (SCM-1.8V), simple current mirrors with 3.3 V transistors (SCM-3.3V) and cascode current mirrors with 3.3 V transistors (CCM-3.3V).

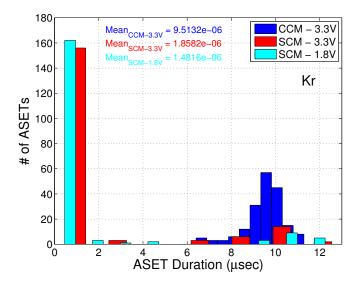

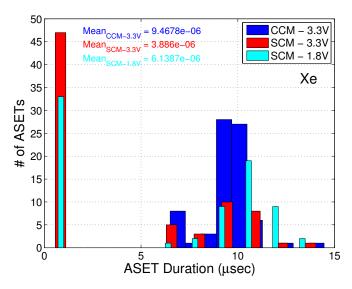

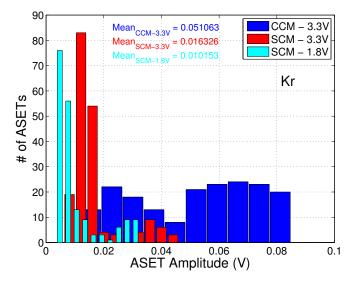

Apart from  $\sigma$ , the duration and amplitude of the ASET is an important factor in RHBD. These results are shown in Figs. 11 and 13 where we analyze and present the first 185 segments recorded for each circuit, while exposed to Kr, and furthermore, in Figs. 12 and 14, where we analyze and present the first 85 segments, recorded for each circuit while exposed to Xe. The measured results of Fig. 11 with Kr ions, show that SCM circuits have smaller average ASET durations, when compared to the CCM circuits. As explained earlier the lower impedance at critical nodes enhances the escape speed of the surplus ionisation charge towards VDD or Ground. The measurements with Xe ions of Fig. 12 show that SCM circuits still exhibit smaller average ASET durations when compared to the CCM circuit. As expected, the average ASET duration of all circuits increases, when compared to the results of Fig. 11 with Kr ions, because of the higher LET of Xe compared to Kr ions.

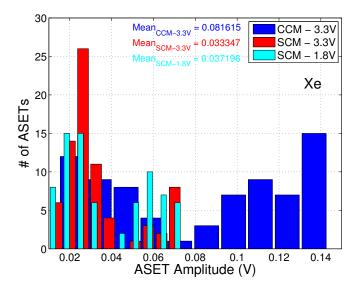

The results of Fig. 13 show that, as with the results of ASET's duration, the SCM topologies exhibit smaller ASETs peak amplitudes when compared to the CCM topology when exposed to Kr ions, with the SCM-1.8V circuit exhibiting the smallest peak amplitudes. This can once again can be explained by the low impedance route to VDD or Ground seen by the excess charge. The measurements of the ASETs average peak amplitudes when the ICs are exposed to Xe ions are shown in Fig. 14. These results agree with the ones of Fig. 13, where the SCM topologies exhibit smaller peak amplitudes compared to the CCM topology. Overall, all circuits exhibit increased ASET amplitudes for Xe compared to Kr irradiation exposure due to increased LET which further perturbs the circuits charge state at particular nodes.

An overall evaluation of the three circuit architectures reveal that the best performance in terms of  $\sigma$  is achieved by the

Fig. 12. Measured number of ASETs Versus ASETs duration for all BGR circuit variants, including simple current mirrors with 1.8 V transistors (SCM-1.8V), simple current mirrors with 3.3 V transistors (SCM-3.3V) and cascode current mirrors with 3.3 V transistors (CCM-3.3V).

Fig. 13. Measured number of ASETs Versus ASETs peak amplitude for all BGR circuit variants, including simple current mirrors with 1.8 V transistors (SCM-1.8V), simple current mirrors with 3.3 V transistors (SCM-3.3V) and cascode current mirrors with 3.3 V transistors (CCM-3.3V).

SCM-3.3V circuit, while the best performance in terms of average ASET duration and amplitude (smaller is better) is achieved by SCM-3.3V and SCM-1.8V which have very similar results. The key factors that affect their performance are the circuit topology, the device gate oxide thickness and the supply voltage. The circuit topology includes, the resistance to VDD/Ground and the sensitive nodes' connections, which in turn affect the time and rate that the generated charge needs to be absorbed, to return to the normal operating conditions. The gate oxide thickness (depends on the type of device that is selected) and the supply voltage, both affect the amount of energy needed in order to alter the transistor's normal operating conditions. In addition, a thinner gate oxide leads to

Fig. 14. Measured number of ASETs Versus ASET's peak amplitude for all BGR circuit variants, including simple current mirrors with 1.8 V transistors (SCM-1.8V), simple current mirrors with 3.3 V transistors (SCM-3.3V) and cascode current mirrors with 3.3 V transistors (CCM-3.3V).

a greater transconductance for a fixed device area, since the channel charge is better controlled. Thus the charge released by an ion at sensitive nodes is amplified and propagated to other adjacent nodes more efficiently in 1.8 V based topologies when compared to 3.3 V topologies, thus affecting the total circuit performance.

Among the designed and tested circuit architectures, the optimal circuit is the SCM-3.3V circuit, because of smaller path resistance to VDD/Ground as opposed to the CCM-3.3V, while it utilizes the 3.3 V transistors which have thicker oxide and higher supply voltage compared to the 1.8 V transistors that are utilized by the SCM-1.8V circuit. The worst circuit in terms of  $\sigma$ , ASET duration and ASET amplitude would marginally be the SCM-1.8V due to the fact that the gate oxide thickness and supply voltage are slightly dominating the ASETs time constant parameters. This is be supported from the results of the Kr ion irradiation. However, it actually turns out that the worst circuit in terms of  $\sigma$  and ASETs duration and amplitude is the CCM-3.3V. This very interesting and important outcome that is revealed from the experimental measurements is originating from pulse quenching that occurs in both the SCM architectures, as opposed to the CCM one.

As BGR circuits' performance is highly dependent on architectural design, such as the topology and the devices parameters, most of the guidelines that are extracted from these experimental results may be used in other analog and mixed signal circuits, intended for the space environment.

### IV. PULSE QUENCHING PHENOMENA IN MEASURED RESULTS

The cross-section of the two variants (SCM-1.8V and SCM-3.3V) of Fig. 1, which utilize simple current mirrors give a seemingly paradoxical response, as is shown in the measured results of Fig. 10. Although Xe ions have a higher LET than Kr ions, the cross-section for Xe-ion-induced ASETs is lower

than the cross-section of Kr-ion-induced ASETs. This paradox can be explained through the pulse quenching phenomenon [2], [64]–[66], which has been previously observed or used to mitigate SETs in other analog or digital circuits such as digital inverters, current sources, switched capacitor amplifiers, continuous time amplifiers, folded cascode amplifiers and differential circuits design [6], [23], [63], [67]–[74]. In the next section we justify the measured results by focussing on the key topological difference between the two circuit classes, i.e. the simple/cascode current mirror.

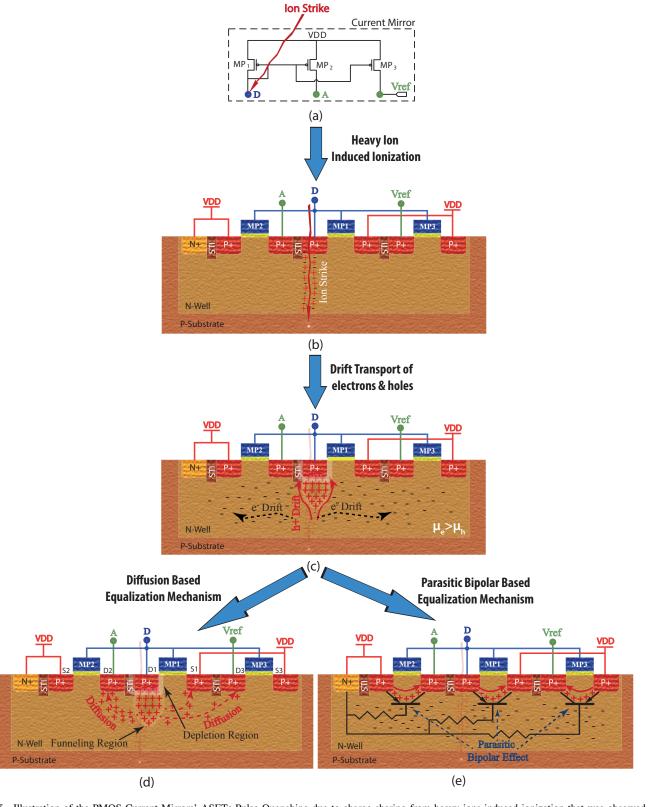

The quenching effect depends heavily on radiation-induced charge sharing. This is the charge interaction of several adjacent circuit nodes *via the substrate* (outside the active channel), instead of *through the the transistors' active channel or via the wiring*. Charge sharing through the substrate induces parasitic currents, which alter the electrical signals that propagate through the intended circuit architecture. Transport outside the active channel consists of two mechanisms: diffusion of the radiation-induced charge within the bulk and charge transport via a parasitic bipolar effect. These two charge sharing mechanisms are explained thoroughly by using Fig. 15, within the context of the current mirror part of the SCM BGR circuits of Fig. 1 and pulse quenching.

The current mirror of this circuit is shown in Fig. 15(a). The most sensitive areas for charge separation of electron-hole pairs are: (a) the depletion region of the reverse biased pn junction of the drain terminal, and (b) the substrate in the close vicinity; thus we analyse the case of energetic ion strikes at node D (drain of MP<sub>1</sub>). However the principles of charge sharing would still apply to strikes in other less sensitive regions.

#### A. Funneling

The physical cross-section of the mirror is shown in Fig. 15(b), including the above mentioned ion strike location and trajectory. Upon impact it transfers enough energy to create a multitude of electron-hole pairs in the region. The high electric fields separate the charges via the drift mechanism and decrease the probability of electron-hole pair recombination. The electric field forces holes to drift towards the drain (funneling mechanism), whilst the electrons are likely to drift towards the n-well substrate bias contacts as illustrated in Fig. 15(c). Due to the difference in mobility, after initial charge separation, a higher concentration of holes remain around the drain terminal therefore extending the collection region relatively far from the drain terminal via funneling drift collection mechanism. Funneling mechanism (based on drift) is much faster compared to the diffusion based mechanism.

#### B. Diffusion Based Equalization Mechanism

The other well-know transport mechanism that affects the charge redistribution is that of diffusion. In Fig. 15(d), the high hole concentration, that is left behind after the electric field has separated the electron-hole pairs, initially increases the voltage at node D, which in turn increases the gate voltage of  $MP_1$ , and therefore the gate voltage of  $MP_2$  and  $MP_3$ . The decreased gate-source voltage ( $V_{GS}$ ) of these devices reduces

Fig. 15. Illustration of the PMOS Current Mirrors' ASETs Pulse Quenching due to charge sharing from heavy ions induced ionization that was observed in the measured results of Fig. 10 and corresponds to the BGR circuit architectures of Fig. 1. (a) Schematic with the current mirror of the Fig. 1 circuit shown in a doted lines box, (b) Ion Strike at node D where it generates an excess of e-h pairs due to ionization along its path (c) The generated e-h pairs start to drift under the electric field (note that mobility of the  $e^-$  is greater than that of holes). Holes drift towards the transistor's drain which is at a lower potential than the N-Well substrate and electrons drift within the N-Well. (d) Charge sharing due to diffusion of holes from the high charge concentration of node A towards the low charge concentration of nodes D(D1),  $V_{ref}(D3)$  and VDD(S1) (diffusion towards this node occurs only if the charge of the excess holes increases beyond that of VDD), (e) Charge sharing due to parasitic bipolar effect (the current direction at  $MP_1$  depends if the radiation-induced charge at node D will be lesser or greater than the charge at VDD).

the current flowing through  $MP_1$ ,  $MP_2$  and  $MP_3$ , and therefore the voltage at nodes A and  $V_{ref}$  will drop. The fact that the substrate under node D has now significantly more charge in comparison to nodes A and  $V_{ref}$ , will trigger a diffusion process of holes from node D towards the adjacent nodes A and  $V_{ref}$  as illustrated in Fig. 15(d). Once the diffused holes are within the vicinity of the reverse biased pn junction of nodes A and  $V_{ref}$ , they are swept across the depletion region, thus increasing the node voltages, and 'quenching' the initial effect of the transient. Hence, the end result of the diffusion of the positive charge through the substrate will be to partially or totally restore the charge disturbance that was induced from the ion strike at nodes A, D and  $V_{ref}$  through this charge redistribution. This effect is highly dependent on the transistor spacing/concentration gradients, and thus was first observed in a  $0.13\mu m$  [63]. The diffusion rate is a function of the charge concentration gradient, therefore with increasing LET the diffusion rate increases, draining via D1 (see Fig.15(d)). If only this phenomenon was at play, the Cross-Section  $\sigma$  would be monotonic i.e. first derivative is positive, but decreasing in value. In order to explain the non-monotonic function of  $\sigma$  Vs LET, Fig. 10, something else is happening. It is either due to the fact that once the hole "cloud" passes the STI barrier a second pn junction D2 assists in the charge draining process, hence enabling a non-monotonic Cross-Section  $\sigma$ , since the drainage capacity doubles. Even though junction S1 is at the same potential as the bulk, it will also assist in draining excess positive charge since the concentration of free holes at the depletion region interface is lower, due to the built in potential, that sweeps the holes from the n-region to the pregion. Furthermore the non-monotonic function of  $\sigma$  Vs LET, could be assisted by the Parasitic Bipolar Based Equalization Mechanism.

#### C. Parasitic Bipolar Based Equalization Mechanism

The parasitic bipolar effect is an additional effect that involves charge draining after a charged ion strike [12], [65], [66], [71], [74], [75]. Parasitic bipolar effect is the process where a PMOS transistor's junction between the P+ source and the N-well is forward biased, resulting in a P-N-P parasitic bipolar junction transistor through the PMOS substrate to be turned on. Thus, through this parasitic BJT, the PMOS source will inject holes to the PMOS drain through the Nwell. This effect, involves charge sharing, not between multiple transistors' terminals like the diffusion process, but between the terminals within a single transistor. The electrons that drift in the bulk due to ionization are confined within the N-Well, thus they will temporarily cause the N-Well potential to drop. This may force the junction between the P+ source and the N-Well to be forward biased, resulting in a P-N-P parasitic bipolar junction transistor through the PMOS N-Well to be turned on as shown in Fig. 15(e). The PMOS source, drain and N-Well bulk will act as a P-N-P bipolar transistor's emitter, collector and base respectively, allowing a flow of holes from source (emitter) to the drain (collector) via the N-Well (base). As a consequence, node D will collect more charge through holes injection from the supply aggravating its charge state,

while nodes A and  $V_{ref}$  will collect charge through holes from the supply thus partially recovering their charge state.

The parasitic bipolar transistors at nodes A and  $V_{ref}$  have a certain threshold where the voltage at the base is greater than that of the emitter and smaller than that of the collector  $(V_E > V_B > V_C)$ . This will occur in relatively high LETs where the BJT base voltage will drop below the emitter one (due to ionized  $e^-$  drift in the N-Well) while concurrently the BJT base voltage will get higher than that of the collector one (due to the decrease charge at nodes A and  $V_{ref}$  caused by the reduction of  $V_{GS}$  of the current mirror). When this threshold is valid then the parasitic BJT enters the active region where the parasitic transistor acts as an amplifier. Therefore the effect of radiation induced  $e^-$  in the N-Well is restoring the radiation induced charge disturbance with an amplification. This amplification can also explain the nonmonotonic function of  $\sigma$  versus LET in the measured results of Fig. 10. Therefore, above a certain LET threshold (ionized electrons-holes pairs is proportional to LET) the  $\sigma$  begin to decline albeit of the higher charge release in the sensitive node.

#### D. The Effect of Pulse Quenching on Simple and Cascode Current Mirrors

In Section III the effect of the cascode mirrors on the SETs was explained in terms of a higher impedance path for the excess charge to be routed to the supply rails. Quenching is also affected by the cascode devices, since even if a second pn junction, like the example of S1, assists in the charge draining process, the extra charge will have to pass through a second transistor, via the normal operating path, and be limited by the saturation current. In order to verify the hypothesis that the decrease in output disturbance at larger LETs can be attributed to Pulse Quenching, a SPICE simulation in Cadence was utilized. Without pulse quenching, a double exponential pulse charge was injected in both the simple current mirror and the cascode current mirror at the key node being node D of Fig. 15(a). For examining the effect of Quenching, a second, smaller double exponential pulse was applied to the second key node, being node A of Fig. 15(a), emulating the charge sharing effect from node D towards node A. The results are shown in of Fig. 16 where both implementations improved in terms of duration and amplitude due to charge sharing enhancement. The simple current mirror is more robust in terms of both cases, with or without pulse quenching. The results show that the simple current mirror circuit's ASET amplitude and duration are reduced to half of the non-quenched. However the cascode current mirror circuit has a minor amplitude reduction which is far larger compare to the simple current mirror one. This suggests that pulse quenching is more advantageous in non-cascode circuit nodes for diminishing or completely eliminating the ASETs.

Pulse quenching in current mirrors can occur under a number of conditions that have to concurrently be valid. These conditions involve the small spacing between the transistors that facilitate charge sharing, the absence of guard ring between those transistors, the LET, the layout design and the circuit architecture. The layouts of the current mirrors that are utilized

Fig. 16. Comparison of a simple current mirror and a cascode current mirror output through SPICE simulations, with and without pulse quenching phenomena.

in the circuits that are reported in this paper were designed in common centroid configurations with multiple fingers for improved transistor matching. In addition to matching issues that are of critical importance in the performance of current mirrors, the matching techniques and common centroid layout will facilitate the charge sharing [76] between the current mirrors during ion strikes in space. This is justified by the fact that in common-centroid layout the mirroring transistors are designed in pairs with minimum distance from each other and they have a common guard ring around them, without any guard ring in between them. The observations revealed from these designs and experimental tests are applicable for current mirrors in all analog and mixed signal integrated circuits.

#### V. CONCLUSION

Radiation sensitivity for high performance deep-submicron IC technologies is expected to be mainly determined by radiation induced ASETs due to continuous shrinking of the devices' feature size and reduced supply voltage. Thus, lower required ion energies will have higher probability to induce ASETs in a circuit node that will propagate to a circuit's output and corrupt the performance of the subsequent circuits, deteriorating the performance of whole system. In order to extract guidelines for mitigating ASETs radiation effects, three BGR circuit variants were designed in 0.18  $\mu$ m CMOS technology, fabricated and characterised against heavyion induced ASETs. After thorough data processing of the measured results, some useful practices were extracted that can be used by designers in order to mitigate SEEs when designing for space electronics. These practices indicate that a better ASET performance can be achieved whilst using devices with thicker oxides, higher supply voltage and fewer cascode stages. Finally, a very important finding suggest that the indispensable current mirrors designed in modern technologies, that are widely used in all analog and mixed signal circuits, can be designed such that they will assist charge sharing that will

subsequently trigger pulse quenching. Thus charge sharing, which in many cases is undesirable, in current mirrors is shown to be extremely beneficial for ASETs mitigation or complete compensation as demonstrated in this paper and could be extended in other analog circuit blocks depending on the circuit architecture and the nature of the electrical coupling between proximal circuit nodes. Based on the measured as well as the simulated results, charge sharing can be utilized as a RHBD technique [56], [67]–[69] for one of the most fundamental analog building blocks, the current mirror.

#### ACKNOWLEDGMENT

This work was supported by European Union SkyFlash Project 262890 FP7-SPACE-2010-1 (SPA.2010.2.2-01 Space Technologies).

This work was supported by the European Space Agency (ESA/ESTEC Contract 4000111630/14/NL/PA) and the Academy of Finland under the Finnish Centre of Excellence Programme 2012-2017 (Project No 2513553, Nuclear and Accelerator Based Physics).

#### REFERENCES

- [1] E. Stassinopoulos and J. P. Raymond, "The space radiation environment for electronics," *Proceedings of the IEEE*, vol. 76, no. 11, pp. 1423–1442, Nov 1988.

- [2] N. M. Atkinson, J. R. Ahlbin, A. F. Witulski, N. J. Gaspard, W. T. Holman, B. L. Bhuva, E. X. Zhang, L. Chen, and L. W. Massengill, "Effect of transistor density and charge sharing on single-event transients in 90-nm bulk CMOS," *IEEE Trans. Nucl. Sci.*, vol. 58, no. 6, pp. 2578–2584, Dec. 2011.

- [3] S. Buchner and D. McMorrow, "Single-event transients in bipolar linear integrated circuits," *IEEE Trans. Nucl. Sci.*, vol. 53, no. 6, pp. 3079– 3102, Dec. 2006.

- [4] J. R. Ahlbin, S. Member, M. J. Gadlage, N. M. Atkinson, B. Narasimham, B. L. Bhuva, S. Member, A. F. Witulski, W. T. Holman, P. H. Eaton, and L. W. Massengill, "Effect of multiple-transistor charge collection on single-event transient pulse widths," *IEEE Trans. Dev. Mat. Rel.*, vol. 11, no. 3, pp. 401–406, Sep. 2011.

- [5] A. Javanainen, S. Member, J. R. Schwank, M. R. Shaneyfelt, R. Harboesørensen, A. Virtanen, H. Kettunen, S. M. Dalton, P. E. Dodd, S. Member, and A. B. Jaksic, "Heavy-ion induced charge yield in MOSFETs," *IEEE Trans. Nucl. Sci.*, vol. 56, no. 6, pp. 3367–3371, Dec 2009.

- [6] T. Kato, T. Uemura, H. Mori, Y. Ikeda, K. Suzuki, S. Satoh, and H. Matsuyama, "Impact of parasitic bipolar effect on single-event upset in p-type metaloxidesemiconductor field effect transistor with embedded SiGe," *Japanese Journal of Applied Physics*, vol. 52, no. 4S, p. 04CC15, March 2013.

- [7] M. Nicolaidis, Ed., Soft Errors in Modern Electronic Systems, ser. Frontiers in Electronic Testing. Springer US, 2011, vol. 41.

[8] J. Benedetto and H. Boesch, "The relationship between 60Co and 10

- [8] J. Benedetto and H. Boesch, "The relationship between 60Co and 10 KeV x-ray damage in MOS devices," *IEEE Trans. Nuc. Sci.*, vol. 33, pp. 1318–1324, Dec 1986.

- [9] R. Lacoe, "CMOS scaling, design principles and hardening-by-design methodologies," in *Short Course presented at the Nuclear and Space Radiation Effects Conference*, Monterey, California, Jul. 2003.

- [10] A. Javanainen, "Particle radiation in microelectronics," Ph.D. dissertation, University of Jyvaskyla, Jyvaskyla, Finland, 2012. [Online]. Available: http://www.jyu.fi/static/fysiikka/vaitoskirjat/2012/Javanainen-Arto-2012.pdf

- [11] R. C. Baumann, "Single event effects in advanced CMOS technology," in *IEEE Nuclear and Space Radiation Effects Conf. Short Course Text*, 2005, pp. 1–59.

- [12] J. R. Ahlbin, "Characterization of the mechanisms affecting single-event transients in sub-100 nm technologies," Ph.D. dissertation, Vanderbilt University, Nashville, Tennessee, May 2012. [Online]. Available: http://etd.library.vanderbilt.edu/available/etd-04012012-154436

- [13] T. Wang, "Study of single-event transient effects on analog circuits," Ph.D. dissertation, University of Saskatchewan, Saskatoon, Saskatchewan, Canada, Aug. 2011. [Online]. Available: http://ecommons.usask.ca/handle/10388/ETD-2011-08-45

- [14] H. Quinn, D. Black, W. Robinson, and S. Buchner, "Fault simulation and emulation tools to augment radiation-hardness assurance testing," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 3, pp. 2119–2142, June 2013.

- [15] H. Quinn, "Challenges in testing complex systems," *IEEE Trans. Nucl. Sci.*, vol. 61, no. 2, pp. 766–786, April 2014.

- [16] S. Gerardin, M. Bagatin, A. Paccagnella, K. Grurmann, F. Gliem, T. Oldham, F. Irom, and D. Nguyen, "Radiation effects in flash memories," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 3, pp. 1953–1969, June 2013.

- [17] V. Ferlet-Cavrois, L. Massengill, and P. Gouker, "Single event transients in digital CMOS - a review," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 3, pp. 1767–1790, June 2013.

- [18] V. Ferlet-Cavrois, P. Paillet, D. McMorrow, N. Fel, J. Baggio, S. Girard, O. Duhamel, J. Melinger, M. Gaillardin, J. Schwank, P. Dodd, M. Shaneyfelt, and J. Felix, "New insights into single event transient propagation in chains of inverters evidence for propagation-induced pulse broadening," *IEEE Trans. Nucl. Sci.*, vol. 54, no. 6, pp. 2338–2346, Dec 2007.

- [19] P. Adell, R. Schrimpf, H. Barnaby, R. Marec, C. Chatry, P. Calvel, C. Barillot, and O. Mion, "Analysis of single-event transients in analog circuits," *IEEE Trans. Nucl. Sci.*, vol. 47, no. 6, pp. 2616–2623, Dec 2000.

- [20] F. Roig, L. Dusseau, A. Khachatrian, N.-H. Roche, A. Privat, J.-R. Vaille, J. Boch, J. Warner, F. Saigne, S. Buchner, D. McMorrow, P. Ribeiro, G. Auriel, B. Azais, R. Marec, P. Calvel, F. Bezerra, and R. Ecoffet, "Modeling and investigations on TID-ASETs synergistic effect in LM124 operational amplifier from three different manufacturers," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 6, pp. 4430–4438, Dec 2013.

- [21] C.-H. Chen, P. Knag, and Z. Zhang, "Characterization of heavy-ion-induced single-event effects in 65nm bulk CMOS ASIC test chips," *IEEE Trans. Nucl. Sci.*, vol. 61, no. 5, pp. 2694–2701, Oct 2014.

- [22] M. Hofbauer, K. Schweiger, H. Zimmermann, U. Giesen, F. Langner, U. Schmid, and A. Steininger, "Supply voltage dependent on-chip singleevent transient pulse shape measurements in 90-nm bulk CMOS under alpha irradiation," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 4, pp. 2640–2646, Aug 2013.

- [23] N. Atkinson, R. Blaine, J. Kauppila, S. Armstrong, T. Loveless, N. Hooten, W. Holman, L. Massengill, and J. Warner, "RHBD technique for single-event charge cancellation in folded-cascode amplifiers," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 4, pp. 2756–2761, Aug 2013.

- [24] V. Lalucaa, V. Goiffon, P. Magnan, G. Rolland, and S. Petit, "Single-event effects in CMOS image sensors," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 4, pp. 2494–2502, Aug 2013.

- [25] M. Gadlage, P. Gouker, B. Bhuva, B. Narasimham, and R. Schrimpf, "Heavy-ion-induced digital single event transients in a 180 nm fully depleted SOI process," *IEEE Trans. Nucl. Sci.*, vol. 56, no. 6, pp. 3483– 3488, Dec 2009.

- [26] G. Anelli, M. Campbell, M. Delmastro, F. Faccio, S. Floria, A. Giraldo, E. Heijne, P. Jarron, K. Kloukinas, A. Marchioro, P. Moreira, and W. Snoeys, "Radiation tolerant VLSI circuits in standard deep submicron CMOS technologies for the LHC experiments: practical design aspects," *IEEE Trans. Nucl. Sci.*, vol. 46, no. 6, pp. 1690–1696, Dec 1999.

- [27] V. Ferlet-Cavrois, "Electronic radiation hardening radiation hardness assurance and technology demonstration activities," in *JUICE Instrument Workshop*, 2011.

- [28] R. A. Reed, "Fundamental mechanisms for single particle-induced soft errors," in NSREC Short Course, 2008.

- [29] T. R. Oldham, "Scaling and single event effects (SEE) sensitivity," in NSREC Short Course, 2003.

- [30] R. Harboe-Sorensen, F.-X. Guerre, H. Constans, J. van Dooren, G. Berger, and W. Hajdas, "Single event transient characterisation of analog IC's for ESA's satellites," in *Proc. Fifth European Conference* on Radiation and Its Effects on Components and Systems (RADECS), 1999, pp. 573–581.

- [31] S. Gerardin, M. Bagatin, A. Paccagnella, A. Visconti, M. Bonanomi, F. Pellizzer, M. Vela, and V. Ferlet-Cavrois, "Single event effects in 90nm phase change memories," *IEEE Trans. Nucl. Sci.*, vol. 58, no. 6, pp. 2755–2760, Dec 2011.

- [32] J. Schwank, M. Shaneyfelt, and P. Dodd, "Radiation hardness assurance testing of microelectronic devices and integrated circuits: Test guideline for proton and heavy ion single-event effects," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 3, pp. 2101–2118, June 2013.

- [33] P. Adell, R. Schrimpf, C. Cirba, W. Holman, X. Zhu, H. Barnaby, and O. Mion, "Single event transient effects in a voltage reference," *Microelectronics Reliability*, vol. 45, no. 2, pp. 355 – 359, Feb 2005.

- [34] F. Irom, T. Miyahira, P. Adell, J. Laird, B. Conder, V. Pouget, and F. Essely, "Investigation of single-event transients in linear voltage

- regulators," *IEEE Trans. Nucl. Sci.*, vol. 55, no. 6, pp. 3352–3359, Dec 2008.

- [35] M. Savage, J. Titus, T. Turflinger, R. Pease, and C. Poivey, "A comprehensive analog single-event transient analysis methodology," *IEEE Trans. Nucl. Sci.*, vol. 51, no. 6, pp. 3546–3552, Dec 2004.

- [36] C. Poivey, J. Howard, S. Buchner, K. LaBel, J. Forney, H. Kim, and A. Assad, "Development of a test methodology for single-event transients (sets) in linear devices," *IEEE Trans. Nucl. Sci.*, vol. 48, no. 6, pp. 2180–2186, Dec 2001.

- [37] D. Fleetwood, M. Rodgers, L. Tsetseris, X. Zhou, I. Batyrev, S. Wang, R. Schrimpf, and S. Pantelides, "Effects of device aging on microelectronics radiation response and reliability," *Microelectronics Reliability*, vol. 47, no. 7, pp. 1075 – 1085, 2007.

- [38] W. Chen, N. Varanasi, V. Pouget, H. Barnaby, B. Vermeire, P. Adell, T. Copani, and P. Fouillat, "Impact of VCO topology on SET induced frequency response," *IEEE Trans. Nucl. Sci.*, vol. 54, no. 6, pp. 2500– 2505, Dec 2007.

- [39] V. Ferlet-Cavrois, D. McMorrow, D. Kobayashi, N. Fel, J. Melinger, J. Schwank, M. Gaillardin, V. Pouget, F. Essely, J. Baggio, S. Girard, O. Flament, P. Paillet, R. Flores, P. Dodd, M. Shaneyfelt, K. Hirose, and H. Saito, "A new technique for SET pulse width measurement in chains of inverters using pulsed laser irradiation," *IEEE Trans. Nucl. Sci.*, vol. 56, no. 4, pp. 2014–2020, Aug 2009.

- [40] F. Roig, L. Dusseau, P. Ribeiro, G. Auriel, N.-H. Roche, A. Privat, J.-R. Vaille, J. Boch, F. Saigne, R. Marec, P. Calvel, F. Bezerra, R. Ecoffet, and B. Azais, "The role of feedback resistors and TID effects in the ASET response of a high speed current feedback amplifier," *IEEE Trans. Nucl. Sci.*, vol. 61, no. 6, pp. 3201–3209, Dec 2014.

- [41] C. M. Andreou, S. Koudounas, and J. Georgiou, "A novel wide-temperature-range, 3.9ppm/°C CMOS bandgap reference circuit," *IEEE J. Solid-State Circuits*, vol. 47, no. 2, pp. 574–581, Jan. 2012.

- [42] Y. P. Tsividis, "Accurate analysis of temperature effects in  $I_c$ – $V_{be}$  characteristics with application to bandgap reference sources," *IEEE J. Solid-State Circuits*, vol. 15, no. 6, pp. 1076 1084, Dec. 1980.

- [43] P. Malcovati, F. Maloberti, C. Fiocchi, and M. Pruzzi, "Curvature-compensated BiCMOS bandgap with 1-V supply voltage," *IEEE J. Solid-State Circuits*, vol. 36, no. 7, pp. 1076–1081, Jul. 2001.

- [44] G. A. Rincon-Mora and P. E. Allen, "A 1.1-V current-mode and piecewise-linear curvature-corrected bandgap reference," *IEEE J. Solid-State Circuits*, vol. 33, no. 10, pp. 1551 –1554, Oct. 1998.

- [45] P. Moreira, "Radiation effects on the "CERN\_bandgap" circuit," Private Communication, 2004.

- [46] C. M. Andreou, A. Paccagnella, D. M. Gonzalez-Castano, F. Gomez, V. Liberali, A. V. Prokofiev, C. Calligaro, A. Javanainen, A. Virtanen, D. Nahmad, and J. Georgiou, "A subthreshold, low-power, RHBD reference circuit, for earth observation and communication satellites," in IEEE International Symposium on Circuits and Systems (ISCAS), 2015.

- [48] B. McCue, B. Blalock, C. Britton, J. Potts, J. Kemerling, K. Isihara, and M. Leines, "A wide temperature, radiation tolerant, CMOS-compatible precision voltage referencefor extreme radiation environment instrumentation systems," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 3, pp. 2272–2279, June 2013.

- [49] Y. Piccin, H. Lapuyade, Y. Deval, C. Morche, J.-Y. Seyler, and F. Goutti, "Radiation-hardening technique for voltage reference circuit in a standard 130nm CMOS technology," *IEEE Trans. Nucl. Sci.*, vol. 61, no. 2, pp. 967–974, April 2014.

- [50] L. Najafizadeh, S. Phillips, K. Moen, R. Diestelhorst, M. Bellini, P. Saha, J. Cressler, G. Vizkelethy, M. Turowski, A. Raman, and P. Marshall, "Single event transient response of SiGe voltage references and its impact on the performance of analog and mixed-signal circuits," *IEEE Trans. Nucl. Sci.*, vol. 56, no. 6, pp. 3469–3476, Dec 2009.

- [51] C. M. Andreou and J. Georgiou, "An all-subthreshold, 0.75V supply, 2ppm/°C, CMOS voltage reference," in *IEEE International Symposium* on Circuits and Systems (ISCAS), 2013, pp. 1476–1479.

- [52] Y. Osaki, T. Hirose, N. Kuroki, and M. Numa, "1.2-V supply, 100-nW, 1.09-V bandgap and 0.7-V supply, 52.5-nW, 0.55-V subbandgap reference circuits for nanowatt CMOS LSIs," *IEEE J. Solid-State Circuits*, vol. 48, no. 6, pp. 1530–1538, 2013.

- [53] A. Cardoso, P. Chakraborty, N. Karaulac, D. Fleischhauer, N. Lourenco, Z. Fleetwood, A. Omprakash, T. England, S. Jung, L. Najafizadeh, N.-H. Roche, A. Khachatrian, J. Warner, D. McMorrow, S. Buchner, E. X. Zhang, C. X. Zhang, M. McCurdy, R. Reed, D. Fleetwood, P. Paki-Amouzou, and J. Cressler, "Single-event transient and total dose

- response of precision voltage reference circuits designed in a 90-nm SiGe BiCMOS technology," *IEEE Trans. Nucl. Sci.*, vol. 61, no. 6, pp. 3210–3217, Dec 2014.

- [54] A. Zanshi, S. Buchner, C. Hafer, S. Hisano, and D. B. Kerwin, "Investigation and mitigation of analog SET on a bandgap reference in triple-well CMOS using pulsed laser techniques," *IEEE Trans. Nucl. Sci.*, vol. 58, no. 6, pp. 2570–2577, 2011.

- [55] A. Camplani, S. Shojaii, H. Shrimali, A. Stabile, and V. Liberali, "CMOS IC radiation hardening by design," Facta Universitatis Electronics and Energetics, vol. 27, no. 2, pp. 251–258, Jun. 2014.

[56] R. W. Blaine, "The design of single-event hardened

- [56] R. W. Blaine, "The design of single-event hardened analog and mixed-signal circuits," Ph.D. dissertation, Vanderbilt University, Nashville, Tennessee, May 2014. [Online]. Available: http://etd.library.vanderbilt.edu/available/etd-04072014-110825/

- [57] R. Jacob-Baker, CMOS Circuit Design, Layout, and Simulation. New York: Wiley-IEEE Press, 2010.

- [58] G. A. Rincon-Mora, Voltage References: From Diodes to Precision High-Order Bandgap Circuits. New York: Wiley-IEEE Press, 2001.

- [59] Y. Tsividis and C. McAndrew, Operation and Modelling of the MOS Transistor, 3rd edition. USA: Oxford Series in Electrical and Computer Engineering, 2010.

- [60] F. Wrobel, L. Dilillo, A. Touboul, V. Pouget, and F. Saigne, "Determining realistic parameters for the double exponential law that models transient current pulses," *IEEE Trans. Nucl. Sci.*, vol. 61, no. 4, pp. 1813–1818, Aug 2014.

- [61] K. Moen, L. Najafizadeh, J. Seungwoo, A. Raman, M. Turowski, and J. Cressler, "Accurate modeling of single-event transients in a SiGe voltage reference circuit," *IEEE Trans. Nucl. Sci.*, vol. 58, no. 3, pp. 877–884, June 2011.

- [62] D. Alexandrescu, L. Anghel, and M. Nicolaidis, "Simulating single event transients in VDSM ICs for ground level radiation," *Journal of Electronic Testing*, vol. 20, no. 4, pp. 413–421, Aug 2004.

- [63] J. R. Ahlbin, S. Member, L. W. Massengill, B. L. Bhuva, S. Member, B. Narasimham, M. J. Gadlage, and P. H. Eaton, "Single-event transient pulse quenching in advanced CMOS logic circuits," *IEEE Trans. Nucl. Sci.*, vol. 56, no. 6, pp. 3050–3056, 2009.

- [64] W. Bennett, N. Hooten, R. Schrimpf, R. Reed, R. Weller, M. Mendenhall, A. Witulski, and D. Wilkes, "Experimental characterization of radiationinduced charge sharing," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 6, pp. 4159–4165, Dec 2013.

- [65] O. A. Amusan, "Effects of single-event-induced charge sharing in sub-100 nm bulk CMOS technologies," Ph.D. dissertation, Vanderbilt University, Nashville, Tennessee, May 2009. [Online]. Available: http://etd.library.vanderbilt.edu/available/etd-02162009-141344

- [66] M. Haghi, "Modeling and mitigation of radiation-induced charge sharing effects in advanced electronics," Ph.D. dissertation, University of Southern California, California, May 2012. [Online]. Available: http://digitallibrary.usc.edu/cdm/ref/collection/p15799coll3/id/17193

- [67] R. W. Blaine, N. M. Atkinson, J. S. Kauppila, T. D. Loveless, S. E. Armstrong, W. T. Holman, and L. W. Massengill, "Single-event-hardened CMOS operational amplifier design," *IEEE Trans. Nucl. Sci.*, vol. 59, no. 4, pp. 803–810, Aug 2012.

- [68] R. W. Blaine, S. E. Armstrong, J. S. Kauppila, N. M. Atkinson, B. D. Olson, W. T. Holman, and L. W. Massengill, "RHBD bias circuits utilizing sensitive node active charge cancellation," *IEEE Trans. Nucl. Sci.*, vol. 58, no. 6, pp. 3060–3066, Dec 2011.

- [69] R. W. Blaine, N. M. Atkinson, J. S. Kauppila, S. E. Armstrong, N. C. Hooten, T. D. Loveless, J. H. Warner, W. T. Holman, and L. W. Massengill, "Differential charge cancellation (DCC) layout as an RHBD technique for bulk CMOS differential circuit design," *IEEE Trans. Nucl. Sci.*, vol. 59, no. 6, pp. 2867–2871, Dec 2012.

- [70] N. M. Atkinson, A. F. Witulski, W. T. Holman, J. R. Ahlbin, B. L. Bhuva, and L. W. Massengill, "Layout technique for single-event transient mitigation via pulse quenching," *IEEE Trans. Nucl. Sci.*, vol. 58, no. 3, pp. 885–890, June 2011.

- [71] J. Ahlbin, M. J. Gadlage, D. R. Ball, A. W. Witulski, B. Bhuva, R. Reed, G. Vizkelethy, and L. Massengill, "The effect of layout topology on single-event transient pulse quenching in a 65 nm bulk CMOS process," *IEEE Trans. Nucl. Sci.*, vol. 57, no. 6, pp. 3380–3385, Dec 2010.

- [72] O. Amusan, A. Witulski, L. Massengill, B. Bhuva, P. Fleming, M. Alles, A. Sternberg, J. Black, and R. Schrimpf, "Charge collection and charge sharing in a 130nm CMOS technology," *IEEE Trans. Nucl. Sci.*, vol. 53, no. 6, pp. 3253–3258, Dec 2006.

- [73] O. Amusan, L. Massengill, B. Bhuva, S. DasGupta, A. Witulski, and J. Ahlbin, "Design techniques to reduce SET pulse widths in deepsubmicron combinational logic," *IEEE Trans. Nucl. Sci.*, vol. 54, no. 6, pp. 2060–2064, Dec 2007.

- [74] G. Yang, C. Jian-Jun, H. Yi-Bai, B. L., and B.-W. L., "The dual role of multiple-transistor charge sharing collection in single-event transients," *Chinese Physics B*, vol. 22, no. 4, p. 046103, 2013.

- [75] B. Olson, D. Ball, K. Warren, L. Massengill, N. Haddad, S. Doyle, and D. McMorrow, "Simultaneous single event charge sharing and parasitic bipolar conduction in a highly-scaled SRAM design," *IEEE Trans. Nucl.* Sci., vol. 52, no. 6, pp. 2132–2136, Dec 2005.

- [76] A. Kelly, P. Fleming, W. Holman, A. Witulski, B. Bhuva, and L. Massengill, "Differential analog layout for improved ASET tolerance," *IEEE Trans. Nucl. Sci.*, vol. 54, no. 6, pp. 2053–2059, Dec 2007.