#### **Amit Resh**

# Enforcing Trust for Execution-Protection in Modern Environments

### Amit Resh

## Enforcing Trust for Execution-Protection in Modern Environments

Esitetään Jyväskylän yliopiston informaatioteknologian tiedekunnan suostumuksella julkisesti tarkastettavaksi yliopiston Agora-rakennuksen auditoriossa 3 joulukuun 19. päivänä 2016 kello 12.

Academic dissertation to be publicly discussed, by permission of the Faculty of Information Technology of the University of Jyväskylä, in building Agora, auditorium 3, on December 19, 2016 at 12 o'clock noon.

Enforcing Trust for Execution-Protection in Modern Environments

### Amit Resh

## Enforcing Trust for Execution-Protection in Modern Environments

Editors Timo Männikkö Department of Mathematical Information Technology, University of Jyväskylä Pekka Olsbo, Ville Korkiakangas Publishing Unit, University Library of Jyväskylä

URN:ISBN:978-951-39-6887-8 ISBN 978-951-39-6887-8 (PDF)

ISBN 978-951-39-6886-1 (nid.) ISSN 1456-5390

Copyright © 2016, by University of Jyväskylä

Jyväskylä University Printing House, Jyväskylä 2016

#### **ABSTRACT**

Resh, Amit

Enforcing Trust for Execution-Protection in Modern Environments

Jyväskylä: University of Jyväskylä, 2016, 98 p. (+included articles)

(Jyväskylä Studies in Computing

ISSN 1456-5390; 255)

ISBN 978-951-39-6886-1 (nid.)

ISBN 978-951-39-6887-8 (PDF)

Finnish summary

Diss.

The business world is exhibiting a growing dependency on computer systems, their operations and the databases they contain. Unfortunately, it also suffers from an ever growing recurrence of malicious software attacks. Malicious attack vectors are diverse and the computer-security industry is producing an abundance of behavioral-pattern detections to combat the phenomenon.

Modern processors contain hardware virtualization capabilities that support implementation of hypervisors for the purpose of managing multiple Virtual-Machines (VMs) on a single computer platform. The facilities provided by hardware virtualization grant the hypervisor control of the hardware platform at an effective privilege level that supersedes the OS.

The purpose of this work is to research and develop a methodology based on a thin-hypervisor that exploits the virtues of hardware virtualization for the purpose of protecting a computer system against malicious penetration. To successfully accomplish this, the thin-hypervisor must be guaranteed to be trusted, with respect to its instructions its configuration structures and its true control over the hardware platform. Moreover, it must be able to protect itself indefinitely from subversion. The methodology presented here describes the means to establish a trusted thin-hypervisor and demonstrates how it may be exercised to restrict code execution exclusively to pre-signed, whitelisted, software.

This methodology provides resistance to most APT attack vectors, including those based on zero-day vulnerabilities that may slip under behavioral-pattern radars.

Keywords: cyber protection, APT prevention, hypervisor, thin-hypervisor, virtualization, attestation, trusted computing, whitelisting,

**Author** Amit Resh

Department of Mathematical Information Technology

University of Jyväskylä

Finland

Supervisors Professor Pekka Neittaanmäki

Department of Mathematical Information Technology

University of Jyväskylä

Finland

Doctor Nezer Zaidenberg

Department of Mathematical Information Technology

University of Jyväskylä

Finland

**Reviewers** Adjunct Prof., Dr. Jarmo Siltanen

Director Institute of Information Technology

JAMK University of Applied Sciences

Finland

Dr. Nethanel Gelernter School of Computer Science

The College of Management Academic Studies

Israel

**Opponent** Adjunct Prof., Dr. Jyri Rajamäki

Laurea University of Applied Sciences

Finland

#### **PREFACE**

This research began with the *TrulyProtect* project, funded by TEKES – the Finnish funding agency for Technology and Innovation and the University of Jyväskylä. The project was launched as an effort to achieve commercialization of academic ideas. The author personally joined the *TrulyProtect* project in December 2012. Since, he has been a chief member and contributor to the project team, as well as a major driver of its research and implementation effort. When setting out to explore new alternatives for creating trusted platforms and software protection schemes, the *TrulyProtect* team had only put forth vague goals and could not entirely foresee the final destination, as it needed to navigate uncharted waters. Eventually, the methodology crystalized and the research bore fruit, as described in this work. Funding for the *TrulyProtect* project supported the team's efforts throughout September 2014, after which continued research was based on individual grants and scholarships.

#### **ACKNOWLEDGEMENTS**

I would like to thank my supervisors, Prof. Pekka Neittaanmäki for his guidance, counseling and assistance in navigating the University terrain, as well as Dr. Nezer Zaidenberg, for his constant support, advice and generally nudging me in the right direction.

Likewise, I would like to express my gratitude to the external reviewers, Dr. Jarmo Siltanen and Dr. Nethanel Gelernter, who thoroughly read my work and provided their valuable comments and insights. I express my thanks, as well, to Dr. Jyri Rajamäki, who generously agreed to act as my opponent.

I would also like to thank the TrulyProtect team, Roee Leon and Asaf Algawi for their support in this research project and assistance in co-authoring some of the joint publications included here, and especially so to Dr. Michael Kiperberg, who served as my main research colleague and with whom I could scrutinize and bounce-off ideas and speculations on an almost daily basis.

I am also indebted to the support of the Ellen and Artturi Nyyssönen Foundation, the COMAS Graduate School and the Department of Mathematical Information Technology, which provided financial assistance for this research, for which I am extremely grateful.

I also owe a great thanks to my beloved wife, Racheli, for enduring this effort and me during the seemingly endless months and years, for her love, understanding, moral support and devotion.

Finally, I would like to thank my children Eyal, May and Eran, Racheli's daughters Dana and Noa, as well as my parents Dr. Nura Resh and Dr. Michael Resh, who also provided important comments to my drafts, for their wholehearted encouragement, support and approval.

Jyväskylä December 2016 Amit Resh

#### LIST OF FIGURES

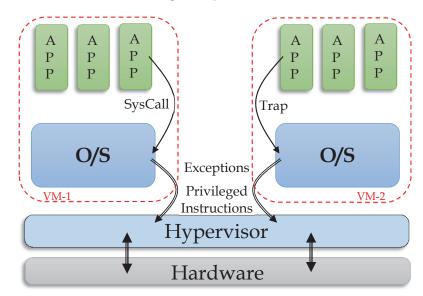

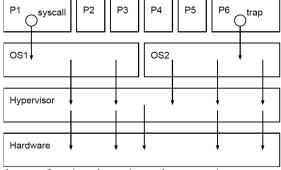

| FIGURE 1 | Virtualized system with 2 Virtual-Machines (VM). Each VM is a stack comprised of an OS with applications running over it. Applications utilize the OS by making system calls and Trap intercepts. Each OS believes to be running over                                                                                                                                                                                                                                                                                                          |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | the hardware platform, however OS requests from the hardware are intercepted and managed by the hypervisor, which maintains isolation between the VMs25                                                                                                                                                                                                                                                                                                                                                                                        |

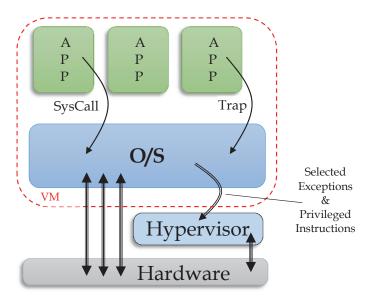

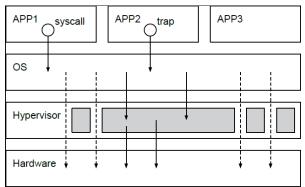

| FIGURE 2 | Thin-hypervisor securing a single VM stack. The thin-<br>hypervisor only virtualizes a select subset of the OS's<br>hardware requests. Most OS operations are executed                                                                                                                                                                                                                                                                                                                                                                         |

|          | directly by the hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

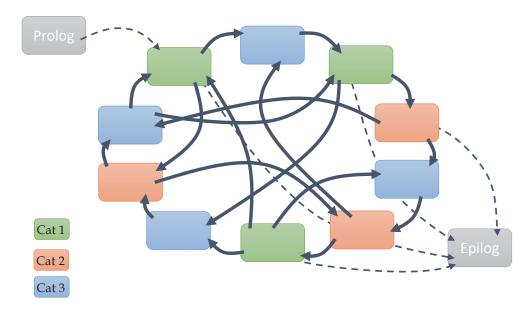

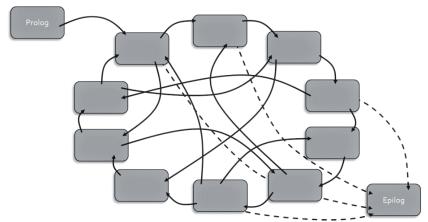

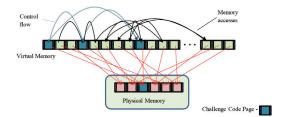

| FIGURE 3 | Challenge Node Network: Note that every circuit includes at least one node of every category. The prolog node executes first; one of several branches transfers control between nodes, according to the current calculation result;                                                                                                                                                                                                                                                                                                            |

|          | the epilog node completes the calculation and terminates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

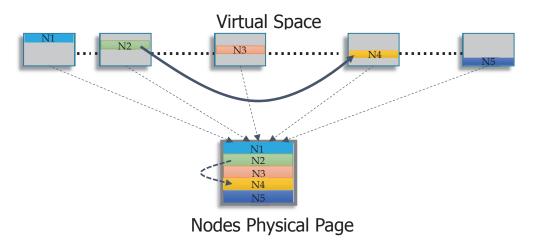

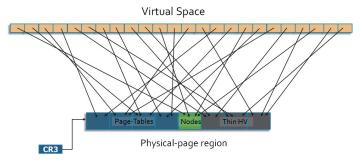

| FIGURE 4 | the challenge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          | by multiple virtual pages. The Page-Tables are a synthetic construct that reflect the virtual mapping. The Nodes page contains the nodes that comprise the challenge and the HDriver pages contain the HDriver's critical function code,                                                                                                                                                                                                                                                                                                       |

|          | whose contents verification is a major goal of the attestation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

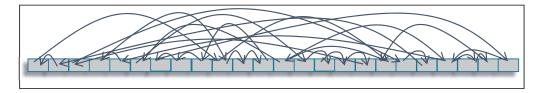

| FIGURE 5 | Pseudo-random walk to scan the virtual memory-space, using the LFSR algorithm. Each word in the virtual-space is                                                                                                                                                                                                                                                                                                                                                                                                                               |

| FIGURE 6 | visited exactly one time in a pseudo random order                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

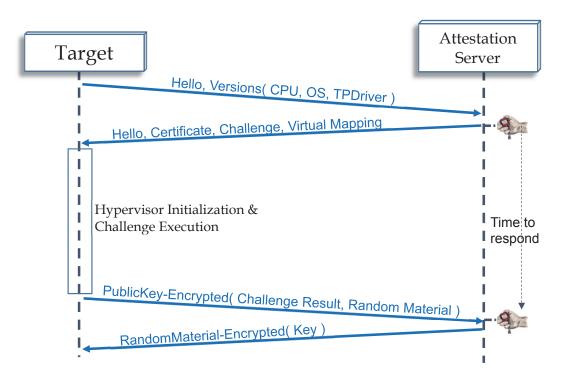

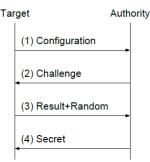

| FIGURE 7 | Four-Way Handshake: Attestation-Server ←→ Target. (I) Target identifies itself and defines its hardware and software platform parameters; (II) Server administers a challenge + Virtual-mapping. It may also identify itself with a certificate; (III) Target responds with challenge result and random material, encrypted with the server's public-key; (IV) If the challenge result checks-out and was replied within the time constraint, the server replies with the secret- key, encrypted with the random material sent to it in packet |

|          | (III)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

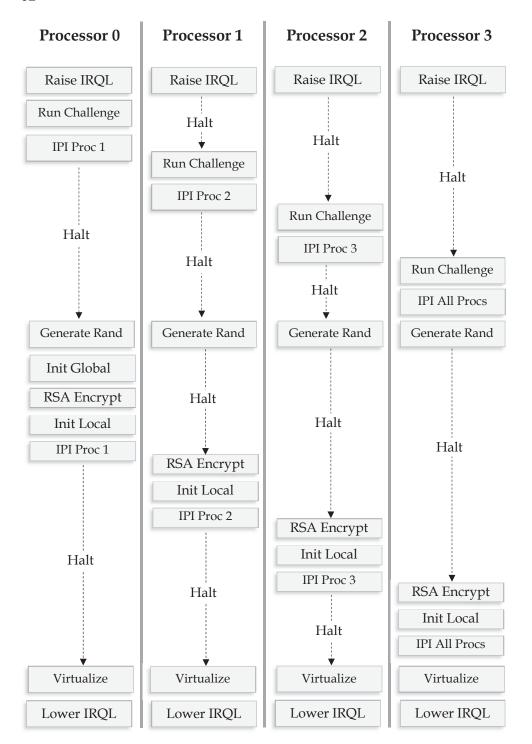

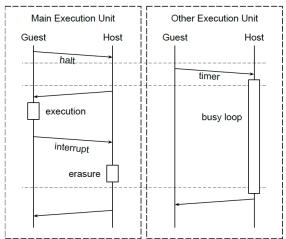

| FIGURE 8               | Timeline diagram of hypervisor initialization critical-<br>section. This scheme ensures that challenge execution and |          |

|------------------------|----------------------------------------------------------------------------------------------------------------------|----------|

|                        | hypervisor configuration occur one core at a time while all                                                          |          |

|                        | other cores are dormant                                                                                              | .52      |

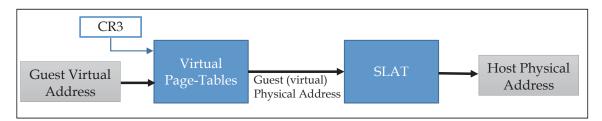

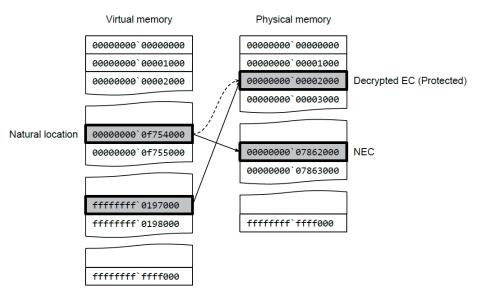

| FIGURE 9               | Translating Guest virtual address to Host physical address with SLAT                                                 | .53      |

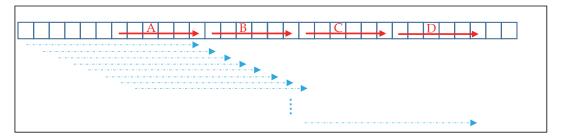

| FIGURE 10              | Pre-calculated challenge results at locations A, B, C and D.                                                         |          |

|                        | During runtime a larger allocation is requested, thus for any                                                        |          |

|                        | available allocation position (as described by the cyan                                                              |          |

|                        | arrows) at least one of the pre-calculated challenge results                                                         |          |

|                        | can be used.                                                                                                         |          |

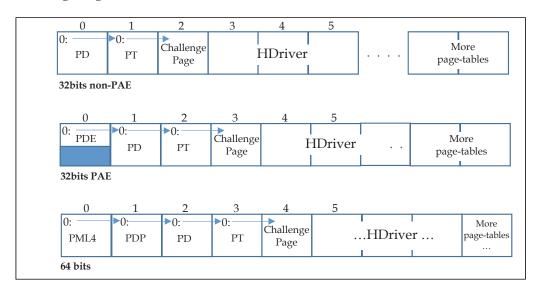

| FIGURE 11              | Three modes of challenge page-tables                                                                                 | .55      |

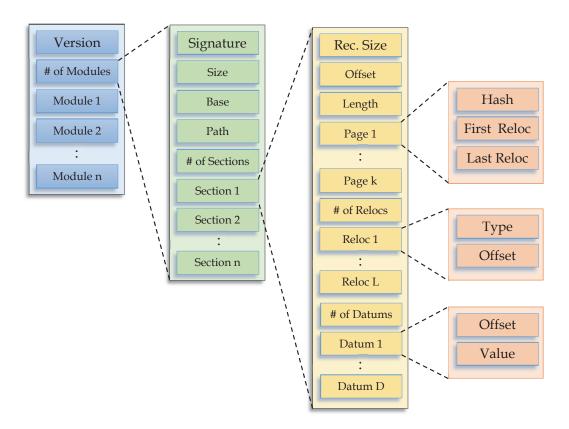

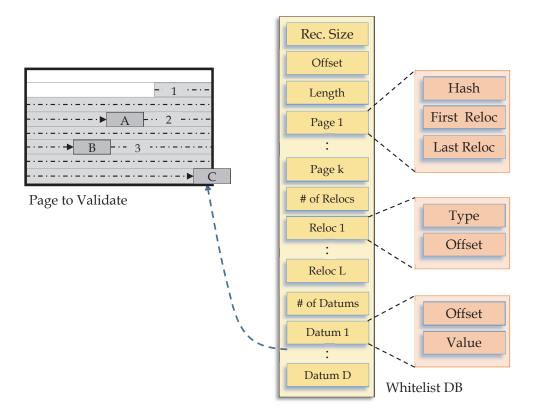

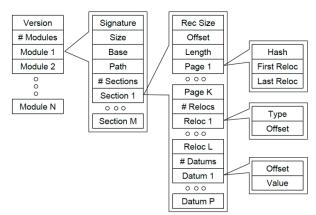

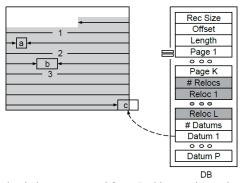

| FIGURE 12              | Database structure of executable code-page hashes. The                                                               |          |

|                        | database includes a section for each executable module.                                                              |          |

|                        | Each module contains an array of sections and each section                                                           |          |

|                        | contains an array of signed executable pages along with the                                                          |          |

| EIGUDE 40              | possible relocation data for each of the pages it contains                                                           | .64      |

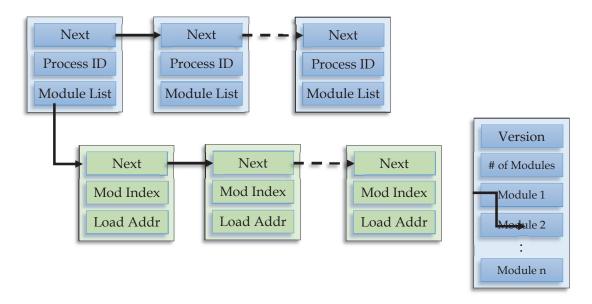

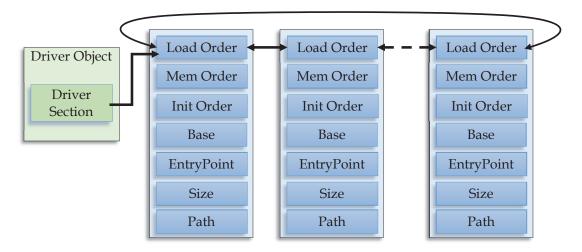

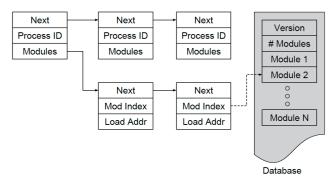

| FIGURE 13              | Process memory-layout data-structure. The structure is a                                                             |          |

|                        | linked-list of processes currently executing in memory. Each                                                         |          |

|                        | process contains a linked-list of all the modules executing                                                          | <b>6</b> |

| EICLIDE 14             | within that process                                                                                                  |          |

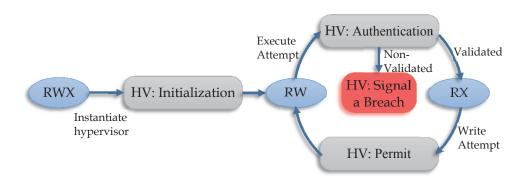

| FIGURE 14<br>FIGURE 15 |                                                                                                                      | .00      |

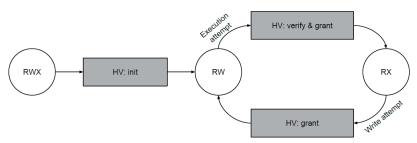

| FIGURE 13              | Physical page access-rights state diagram. Following hypervisor initialization and attestation, all physical pages   |          |

|                        | have R/W access only. Any such page that is executed will                                                            |          |

|                        | cause a hypervisor VM Exit that will validate the page's                                                             |          |

|                        | signature before allowing it R/X access only. An attempt to                                                          |          |

|                        | write to the page will cause a hypervisor VM Exit allowing                                                           |          |

|                        | it to remove Execute access and restoring the page to the                                                            |          |

|                        | initial R/W access rights                                                                                            | .67      |

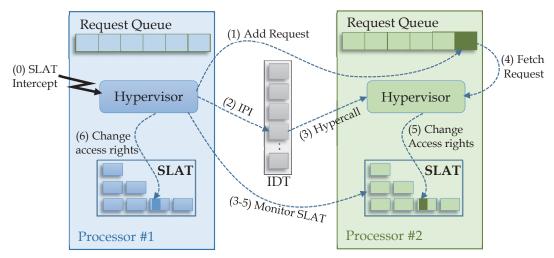

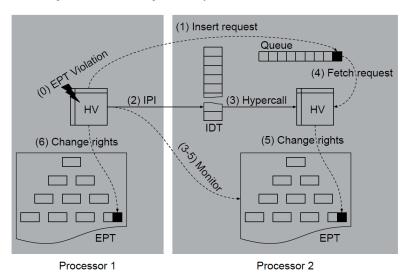

| FIGURE 16              | Access rights modification in a Multiprocessor                                                                       |          |

|                        | environment. Each core has its own SLAT table, therefore                                                             |          |

|                        | changes to the SLAT table in one core must be reflected in                                                           |          |

|                        | the SLAT table of all other cores                                                                                    | .68      |

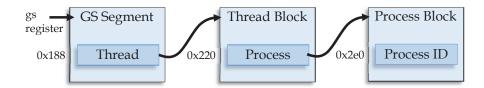

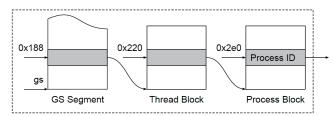

| FIGURE 17              | Windows 8 Process ID location                                                                                        | .70      |

| FIGURE 18              | Page Validation Process. Relocations need to be accounted                                                            |          |

|                        | for. Their location and width in the section is recorded in                                                          |          |

|                        | the database for this purpose. The intended value is also                                                            |          |

|                        | recorded if the relocation field crosses a page boundary to                                                          |          |

|                        | ensure that bytes past the page are not read at a high IRQL                                                          | .71      |

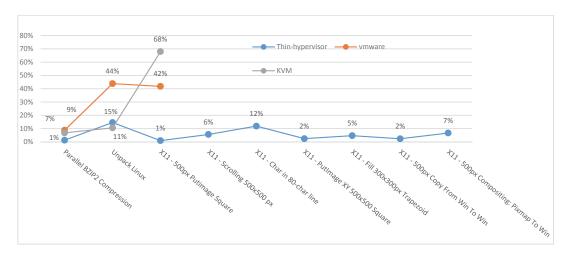

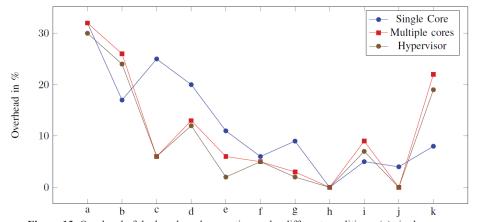

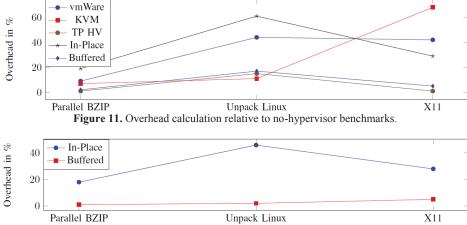

| FIGURE 19              | Hypervisor Performance Overhead Comparison                                                                           |          |

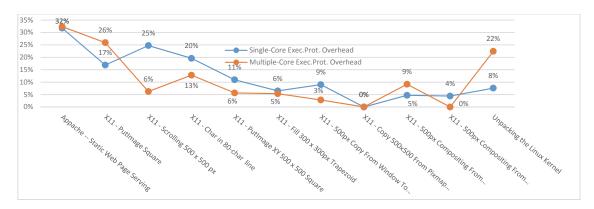

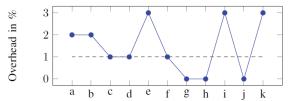

| FIGURE 20              | Execution Protection Overhead                                                                                        | .77      |

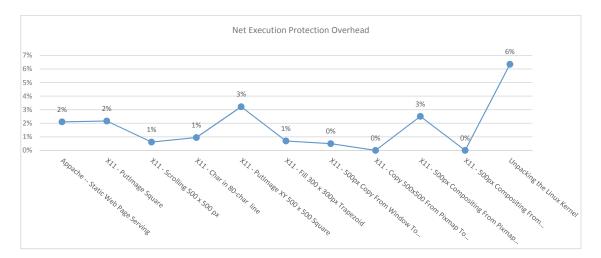

| FIGURE 21              | Net Mutli-Core Execution Protection. Overhead of total                                                               |          |

|                        | execution protection less overhead of an idle hypervisor                                                             | .78      |

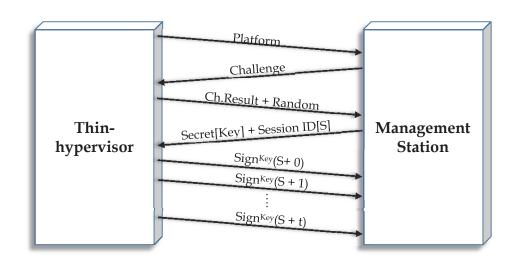

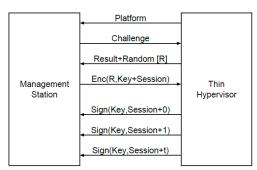

| FIGURE 22              | Protocol between thin-hypervisor and management station.                                                             |          |

|                        | The protocol begins with the 4-way handshake initially                                                               |          |

|                        |                                                                                                                      |          |

| performed to attest the hypervisor and furnish it with secret |     |

|---------------------------------------------------------------|-----|

| information. It is followed by periodic notification from the |     |

| hypervisor to prove that it is continuously functioning, and  |     |

| therefore the system can be considered protected              | .82 |

#### LIST OF TABLES

| TABLE 1 | Node Categories Table                                           | 37 |

|---------|-----------------------------------------------------------------|----|

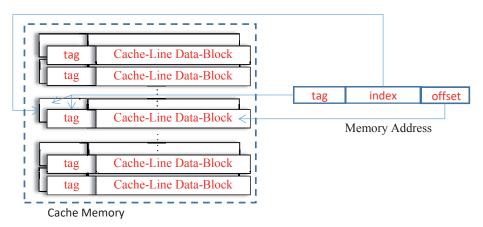

| TABLE 2 | Indexes of cache-lines selected for eviction when accessing a   |    |

|         | 9th cache-line after filling all 8-ways of the cache set        | 44 |

| TABLE 3 | Indexes of cache-lines selected for eviction when accessing a   |    |

|         | 9th cache-line after filling all 8-ways of the cache set with a |    |

|         | preliminary cache-training procedure                            | 45 |

| TABLE 4 | Indexes of cache-lines selected for eviction when accessing a   |    |

|         | 9th cache-line after filling all 8-ways of the cache set        |    |

|         | according to a random sequence and with a preliminary           |    |

|         | cache-training procedure                                        | 46 |

| TABLE 5 | Hypervisor overhead comparison results of various               |    |

|         | Phoronix benchmarks                                             | 75 |

| TABLE 6 | Comparative measurements of standard benchmarks with            |    |

|         | and without execution protection                                | 77 |

#### **CONTENTS**

ABSTRACT

PREFACE

ACKNOWLEDGEMENTS

LIST OF FIGURES

LIST OF TABLES

CONTENTS

LIST OF INCLUDED ARTICLES

| 1 | INT | RODUCTION                                            | 15 |

|---|-----|------------------------------------------------------|----|

|   | 1.1 | Modern System Execution Vulnerabilities              | 15 |

|   | 1.2 | Creating Trust in a Remote System                    |    |

|   | 1.3 | Methods of Obfuscation                               | 18 |

|   | 1.4 | Security by Design                                   | 19 |

|   | 1.5 | Overview of the Proposed Methodology                 | 19 |

|   |     | 1.5.1 Adversary Model                                |    |

|   |     | 1.5.2 Proposed Methodology                           | 20 |

|   |     | 1.5.3 Existing Methodologies Evaluation              | 22 |

|   | 1.6 | Research Contribution                                | 22 |

|   | 1.7 | Author Contribution                                  | 23 |

| 2 | USI | NG A HYPERVISOR TO ENFORCE TRUST                     | 24 |

|   | 2.1 | Hypervisors and Hardware-Assisted Virtualization     | 24 |

|   | 2.2 | The Thin-Hypervisor                                  | 26 |

|   | 2.3 | Attestation of a Remote Hypervisor Activation        | 28 |

|   | 2.4 | Protecting a Thin-Hypervisor that Enforces Trust     | 30 |

|   |     | 2.4.1 Secret Material Storage                        | 31 |

|   |     | 2.4.2 Protecting Hypervisor Configuration-Structures |    |

|   |     | 2.4.3 Using Intel VT-d and AMD-Vi (IOMMU)            | 31 |

|   |     | 2.4.4 Secure AES Cryptography                        | 32 |

|   |     | 2.4.5 Intercepting Critical Instructions             | 32 |

| 3 | REN | MOTE SOFTWARE ATTESTATION METHODOLOGY                | 33 |

|   | 3.1 | Previous Work                                        | 33 |

|   | 3.2 | Attestation Goals                                    | 34 |

|   | 3.3 | Hardware side effects                                | 35 |

|   | 3.4 | Challenges                                           | 36 |

|   |     | 3.4.1 Overview                                       | 36 |

|   |     | 3.4.2 Challenge Construction                         | 37 |

|   |     | 3.4.3 Challenge Repeatability                        | 41 |

|   | 3.5 | Attestation Flow                                     |    |

|   |     | 3.5.1 Overview                                       | 46 |

|   |     | 3.5.2 Hypervisor Initialization                      | 47 |

|   |     | 3.5.3 Challenge Execution                            | 54 |

|   |     |                                                      |    |

|      |            | 3.5.4 Secondary Attestation                                 | 56 |

|------|------------|-------------------------------------------------------------|----|

|      | 3.6        | Secure communications                                       | 56 |

|      | 3.7        | Verifying the Attestation Goals                             | 57 |

| 4    | EXE        | CUTION PROTECTION OF NATIVE CODE                            |    |

|      | 4.1        | Overview of the methodology                                 |    |

|      | 4.2        | Whitelisting an Execution Environment                       |    |

|      | 4.3        | Enforcing Valid Execution of Native Code                    |    |

|      |            | 4.3.1 Initialization                                        |    |

|      |            | 4.3.2 Access Rights Modification                            |    |

|      |            | 4.3.3 Execution Request Verification                        |    |

|      | 4.4        | Special Execution Pages                                     |    |

|      |            | 4.4.1 Mixed Pages                                           | 71 |

|      |            | 4.4.2 Page Modifying Instructions                           | 73 |

|      |            | 4.4.3 Code Pages that Include Data-Sections                 | 73 |

|      |            | 4.4.4 Self-Modifying Code                                   | 73 |

|      | 4.5        | Performance                                                 | 74 |

|      |            | 4.5.1 Hypervisor Overhead                                   |    |

|      |            | 4.5.2 Execution Protection Overhead                         | 75 |

|      | 4.6        | Execution Protection of Interpreted Code                    | 78 |

| 5    | MAI        | NAGEMENT STATION                                            | 80 |

|      | 5.1        | Overview                                                    | 80 |

|      | 5.2        | Management Station Functions                                | 81 |

|      | 5.3        | Updating Software Applications                              | 81 |

|      | 5.4        | Protecting the Management Station                           | 83 |

| 6    | SUM        | IMARY OF ORIGINAL ARTICLES                                  | 84 |

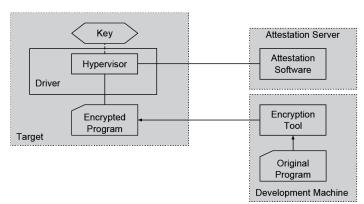

|      | 6.1        | Preventing Execution of Unauthorized Native-Code Software   | 84 |

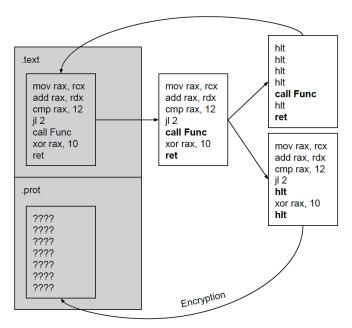

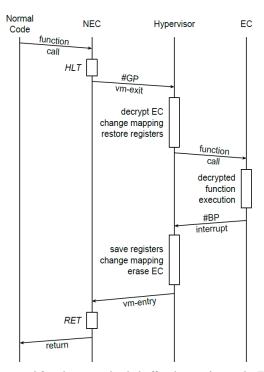

|      | 6.2        | System for Executing Encrypted Native Programs              | 85 |

|      | 6.3        | Remote Attestation of Software and Execution-Environment in | ΩE |

|      | <i>(</i> 1 | Modern Machines                                             |    |

|      | 6.4        | Timing and Side Channel Attacks                             |    |

|      | 6.5        | Trusted Computing and DRM                                   |    |

|      | 6.6        | Can keys be hidden inside the CPU on modern Windows host    |    |

|      | 6.7        | System for Executing Encrypted Java Programs                | 87 |

| 7    |            | ICLUSIONS                                                   |    |

|      | 7.1        | Contributions                                               |    |

|      | 7.2        | Limitations & Future Research                               | 90 |

| YHT  | EEN        | VETO (FINNISH SUMMARY)                                      | 91 |

| REFI | EREN       | ICES                                                        | 92 |

|      |            |                                                             |    |

#### LIST OF INCLUDED ARTICLES

- PI Resh, A.; Kiperberg, M.; Leon, R.; Preventing Execution of Unauthorized Native-Code Software. To be published in: *JDCTA*, *International Journal of Digital Contents Technology and its Applications*, 2016.

- PII Resh, A.; Kiperberg, M.; Leon, R.; Zaidenberg, N.J.. System for Executing Encrypted Native Programs. To be published in: *JDCTA*, *International Journal of Digital Contents Technology and its Applications*, 2016.

- PIII Kiperberg, M.; Resh, A.; Zaidenberg, N.J.. Remote Attestation of Software and Execution-Environment in Modern Machines. *The 2nd IEEE International Conference on Cyber Security and Cloud Computing*, 2015.

- PIV Zaidenberg, N.J.; Resh, A.. Timing and Side Channel Attacks. *Cyber Security: Analytics, Technology and Automation, vol. 78, pp. 183-194,* 2015.

- PV Zaidenberg, N.J.; Neittaanmäki, P.; Kiperberg, M.; Resh, A.. Trusted Computing and DRM. *Cyber Security: Analytics, Technology and Automation, vol. 78, pp.* 205-212, 2015.

- PVI Resh, A.; Zaidenberg, N.J.. Can keys be hidden inside the CPU on modern Windows host. *ECIW* 12th European Conference on Information Warfare and Security, Jyväskylä, 2013.

- PVII Kiperberg, M.; Resh, A.; Algawi, A.; Zaidenberg, N.J.. System for Executing Encrypted Java Programs. 38th IEEE Symposium on Security and Privacy (IEEE S&P 2017), Submitted.

- PVIII Kiperberg, M.; Resh, A.; Algawi, A.; Zaidenberg, N.J.. System for Executing Encrypted Java Programs. 3rd International Conference on Information Systems Security and Privacy (ICISSP 2017), 2017.

#### 1 INTRODUCTION

#### 1.1 Modern System Execution Vulnerabilities

An abundance of malicious software attacks plague the computer software industry. The attack methodologies are diverse, ranging from code-injection, buffer-overflow, viruses, worms and Trojans to rootkits. Malicious code is usually designed to gain access to and steal the victim's data, such as personal information, credentials, trade secrets, or to gain access to the victim's system in order to take advantage of the resource for inflicting further damage. Malicious code motivation is predominantly financial but in some case other motivations may exist as well.

An assortment of recent cases bear witness to this escalating and dire problem:

- Target (Nov 2013): Target is one of the largest discount retailers in USA, second only to Walmart. Malware designed to capture the details of swiped credit cards was installed in Target's payment server just prior to Thanksgiving sales. Roughly 40 million customer credit cards were abducted [1].

- **JP Morgan Chase** (Oct 2014): With assets surpassing \$2 trillion, it is the largest bank in the USA and one of largest in the world. Four hackers penetrated the bank servers and obtained illegal access to over 80 million customer accounts, thereby reaping over \$100M using these for online gambling, phishing and money laundering to name only a few [2].

- Anthem (Feb 2015): The largest health insurance company in the Bluecross Blue-Shield association. In Feb 2015, Anthem reported that its database had been breached and 80M current and past patient credentials and medical data had been exposed [3].

- **Premera Health** (Mar 2015): Premera Health is a large, non-profit, Bluecross Blue-shield health insurance company. The company reported that hackers broke into its database exposing 11 million customer records [4].

- Ashely Madison (July 2015): Ashely Madison is an online dating service geared towards married people looking for an ex-marital relationship. In July 2015 a hacker group calling itself "The Impact Team" hacked Ashely

Madison's computers and stole its entire user base. The group tried to blackmail the site into shutting down and ended up leaking 25 Gigabytes of material when their demands were not met. The data breach caused an immense impact on the lives of the people involved, including two suicides linked to the event [5].

In many cases malicious attacks are not carried out in a single shot. Many attacks are multi-faceted, containing several intermediate steps, each designed to progress the offender to the next level of penetration before reaching the final goal. As an example, SophosLabs [6] details 5 stages of a Web malware attack leading from entry to execution on the compromised system:

**Entry** – malicious code enters the victim system as a result of a drive-by download occurring when visiting a hijacked site or following a malicious link in an Email.

**Traffic Distribution** – Drive-by downloads execute inside browsers. Their primary goal is to download an exploit kit. Traffic redirection occurs to conceal the Host IP address from which the exploit kits are eventually downloaded.

**Exploits** - Once an exploit kit is downloaded it attempts to locate a system vulnerability that it can exploit in order to progress the attack. Exploits are usually encapsulated in PDF, FLASH, Java, JS or HTML files.

**Infection** – Once a vulnerability is found by the exploit kit, it is used to download the actual malware executable code. SophosLabs identify several common malware payloads: Zbot(Zeus) – steals personal information by logging keystrokes and grabbing display frames; Ransomeware – restricting access to the user's resources and demanding payment to restore access; PWS – steals user credentials and allows remote access; Sinowal(Torpig) – installs a rootkit to steal credentials and allow remote access.; FakeAV – a Fake antivirus that "finds" fake viruses and demands payment to "clean" them out.

**Execution** – The downloaded malware has been installed in the victim system and is executed. This is the stage where the actual damage is inflicted.

Other types of attacks exist as well, each seeking to abuse system or human vulnerabilities in order to penetrate a system in order to inflict damages, gain access to privileged information or completely take control. Many of these attacks are similarly multi-stage. Attacks may exploit all or some of the following common stages:

**Entry** - Malicious code enters the system as a result of a malicious Email attachment, a bogus executable installation a buffer-overflow, a USB disk insertion a worm or a virus spreading.

**Non-privileged execution** – In this mode of execution, malicious code that has entered the system executes in a low privileged level. It may still inflict some damage, however that damage is usually limited and may eliminate its capability to achieve persistency. In that case, the malicious code will disappear when the system is rebooted.

Escalation: privileged execution – A much more hazardous case occurs when an un-privileged code exploits a system vulnerability (usually in the O/S) and manages to escalate its privilege. It is beyond the scope of this text to describe the mechanisms that may be employed to achieve this, but the statistics are most staggering. Malicious code that gains privileged access may freely write to the file system on disk – both to user and to OS space, to the system registry or even to the boot record or BIOS memory.

Acquiring Persistency – Using the capabilities of privileged execution, malicious code can strive for persistency. In other words, the capability to survive system reboot as well as a complete system power-cycle. Achieving this level is the first step in securing the malicious code's survival in the compromised system. Many infections will also go to great lengths to camouflage their existence using a variety of methods, some very cunning, to avoid detection and removal.

**Compromised system** – Once malicious code has persistent execution on the system the perpetrator can potentially steal sensitive data, log keyboard activity to steal messages or passwords, grab screen-shots or even achieve full remote-control of the system.

#### 1.2 Creating Trust in a Remote System

In general, achieving *Trust* in remote computer systems should be interpreted as generating a specific instance or object, which can be trusted and relied upon to act in a predetermined way under all circumstances [7]. In general, *Trust* encompasses validated software combined with some secret data known only to that software coupled with a methodology that assures protection against subversion and/or modification of the secret data.

Therefore, *Trust* must be created, validated and then (indefinitely) sustained.

The problem of remote authentication, determining whether a remote computer system is running the correct software version, is well known [8] [9] [10] [11]. Equipped with a remote authentication method, a service provider can prevent unauthenticated remote software from obtaining some secret information or some privileged service. For example, only authenticated gaming consoles can be allowed to connect to the gaming networks [12] [13] and only authenticated bank terminals can be allowed to fetch records from the bank database [14].

The research in this area can be divided into two major branches: hardware assisted authentication [15] [16] and software-only authentication [8] [9]. While in theory, hardware assisted authentication may provide more conclusive results regarding the authenticity of a remote machine, in practice the hardware fails to provide additional security due to inappropriate designs of currently available operating systems [17].

Hardware assisted authentication uses an external hardware component, such as a Trusted Platform Module (TPM), to compute a cryptographic hash of the computer's hardware and software configuration to attest it. Frequently the TPM is used as the root of a chain of trust [18]. The TPM measures the authenticity of the BIOS. The BIOS then measures the authenticity of the boot loader and so on. Unfortunately, all common modern operating systems (e.g. Linux, Windows, OS X) allow the user to load drivers for execution with the same privileges as the operating system itself, i.e. ring 0 on x86 and x64 hardware. Malicious or buggy drivers, which are executed with high privileges, allow random code execution and thus make it possible to circumvent the authenticity measurements of the TPM. Physical attacks on TPM were also shown to exist, assuming the assailant has access to the hardware were it is installed [19] [20] [21].

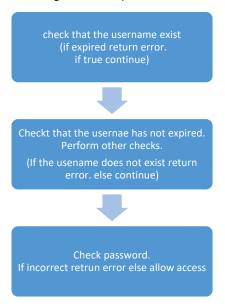

System-wide authentication entails simultaneously authenticating some software component(s) or memory region, as well as verifying that the remote machine is not running in virtual or emulation mode. These methods may also involve a challenge code that is sent by the authentication authority, and executed on the remote system. The challenge code computes a result that is then transmitted back to the authority. The authority deems the entity to be authenticated if the result is correct and was received within a predefined timeframe. The underlying assumption, which is shared by all such authentication methods, is that only an authentic system can compute the correct result within the predefined time-frame. The methods differ in the means by which (and if) they satisfy this underlying assumption.

#### 1.3 Methods of Obfuscation

One way of preventing circumvention of software, is by using methods of obfuscation [22] [23] [24] [25]. The term obfuscation refers to making software instructions difficult for humans to understand by deliberately cluttering the code with useless, confusing pieces of additional software syntax or instructions. Obfuscated code must still be functional, however its goal is to render the code difficult enough to understand and therefore too difficult to reverse-engineer. The assumption is that without properly reverse-engineering software, it is not possible to subvert or circumvent it to the gain of the aggressor. In most cases obfuscation methods attempt to protect two main aspects of malicious attacks: (a) software piracy; and (b) software tampering. Software piracy takes on the form of operating or redistributing software without a license or stealing software intellectual property, such as an algorithm used in a software product. Software tampering involves making changes to existing software, such as circumventing instructions that may check for licensing or by adding instructions that are designed to achieve some malicious activity, such as a virus or any other form of malware that needs to infiltrate the system.

More advanced, software publishers may protect their digital content product by encryption, using a unique key to convert the software code or data to an unreadable format, such that only the owner of the unique key may decrypt the software code. Such protection, however, is only effective when the unique key is kept secured and unreachable to an adversary. This reduces the security issue to that of securing the key. Since the software must also function properly in its untampered form, it must have the key available, leading to the necessity to obfuscate the key and the routines that make use of the key.

It has been shown that obfuscated software code can be invariably broken by hackers, specifically since its content must still be readable to properly function [26] [27] [28] [29] [30]. Hackers equipped with the proper tools, such as disassemblers, logic analyzers, tools for static and dynamic analysis coupled with patience and dedication, have cracked even the most cunning software obfuscations methods.

#### 1.4 Security by Design

Security by design [31] [32] proposes an alternative to methods of obfuscation, which propagate security by obscurity. Rather than attempting to secure a system *after* its implementation, by hiding or obfuscating its critical elements, security by design addresses the issues of security as part of the system design *before* its implementation. Using this approach [33], system design inherently encompasses active security techniques, vulnerability elimination and built-in resistance to attack adhering to best-practices. Security by design steers away from relying on secret operations, obscurity or obfuscation techniques to achieve security. Revealing the security design openly, without compromising its security, often leads to the best security by design methodologies. The reason for this is twofold:

- (a) System security does not rely on chance and is not dependent on as adversary's capability to investigate or stumble upon a secret. Security is fundamental to the methodology, where it can be shown that knowing its inner workings does not compromise it; and

- (b) The security methodology is open to all, for scrutinizing and peerreview, leading to flaws, if any, being exposed and amended.

#### 1.5 Overview of the Proposed Methodology

Protecting computer systems from malicious code, malware and data-breaches in an impregnable manner, must be based on foundations of "security by design". One of the key points in achieving this is successfully creating *trusted components* on the target system. The trusted components are comprised of software and its configuration data. In this context, setting up *trusted software*

on a computer system should be interpreted as software that can be guaranteed to perform in a predetermined manner, whose code contents are validated, that can protect its internal assets (code and data) from subversion and that can perform unique activities (such as cryptographic computations) that prove its authenticity at any time.

#### 1.5.1 Adversary Model

We assume that an adversary is freely able to access system memory for writing and reading. Memory can be accessed for writing in a variety of ways. For example, contents can be loaded from disk, arrive over a communication channel or be injected directly into memory by an executing application. We further assume that an adversary is also able to write to some memory regions that should in principle be protected by the OS, based on exploiting system vulnerabilities. Such regions include, but are not limited to, application code, privileged kernel-mode code and system drivers.

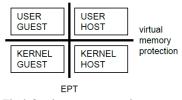

Furthermore, it is assumed that an adversary cannot obstruct the operation of a root (primary) hypervisor based on hardware virtualization. Nor can an adversary obstruct the protected mechanisms of SLAT (secondary level address translation) (i.e., EPT) and IOMMU that operate at a privilege that is higher than the OS while a hypervisor is active.

Adversary attacks that are based on manipulating pure data in memory, in such a way as to render legitimate code malicious (referred to as code-reuse) are not considered.

#### 1.5.2 Proposed Methodology

A general overview of the proposed methodology is presented here which shall be elaborated in detail in the following chapters.

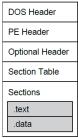

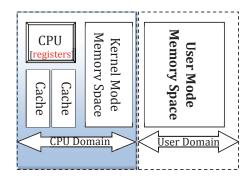

Computer systems that run application software are normally managed by Operating Systems (OS). The OS manages all hardware resources, schedules software for execution and provides hardware-oriented services [34] [35] to the applications that run above it. Since the OS is an intermediary between the hardware and the software, it must have full control over the hardware resources to properly manage and allocate them to the software applications in such a manner so as to maintain system integrity. As such, OS software routines must be given a higher privilege level than the application software. The elevated privilege assures that application software cannot circumvent the OS in accessing the hardware or software resources, which must be exclusively controlled by the OS. For this purpose, the central core of the OS, called the Kernel [36] [34], is composed of a group of routines that operate at an elevated privilege level. The Kernel routines carry out all the hardware and critical software management task. In modern processors, privilege level is enforced by a set of instructions that can only be performed when the processor is put in a high privilege mode. The OS configures the system so that only the kernel routines operate at the higher privilege mode, while all other software applications operate at a lower privilege level and thus require kernel routine assistance in utilizing hardware resources.

A critical security restriction, that must be enforced, is ensuring that malware does not infiltrate the OS kernel and can thus execute at an elevated privilege level, consequently allowing it to obtain full control of the computer system. However, this is easier said than done. Due to the size and complexity of operating systems, hackers and malware programmers are continuously finding vulnerabilities that are exploited to allow malicious software to gain a high privilege level and compromise the system. Therefore, the methodology proposed herein suggests the use of a software component having a higher privilege than the OS. Thus, it can be used to manage system security, even in light of the possibility that malware has infiltrated the kernel and achieved OS privilege level execution rights.

The embodiment of a software component with privileges higher than the OS has been realized in the form of a hypervisor [37] [38] and is used to manage several operating systems on a single hardware platform. Hypervisors, first introduced in mainframe computers in the 1960s, now utilize hardware virtualization [39] that is available in most modern processors.

Rather than use a hypervisor as a multi-operating-system manager, it is proposed to utilize its elevated privilege to manage and monitor a systems security. However, to achieve that, the hypervisor itself must be guaranteed to be *trusted* and completely free of malware and vulnerability to subversion. Two main aspects of hardware virtualization technology position the hypervisor as a favorable candidate for a software component that can be remotely trusted to be safe. First, a minimal hypervisor can be created and therefore with minimal complexity, making it easier to verify. And second, once a verified (and authenticated) hypervisor is in control of a hardware platform it is potentially able to resist all attempts of subversion.

The proposed methodology, described in this work, proposes to run a minimal hypervisor for the sole purpose of securing a computer system. Furthermore, an *attestation* procedure [8] [40], governed by an external server system, is used to ensure that the hypervisor is trustworthy by authenticating and validating its contents. The attestation procedure will serve to guarantee that a hypervisor, after taking control of a remote system, is trustworthy and can be safely assumed to maintain its trustworthiness so-long as the system remains in operation. Once trustworthiness is established, the attestation server can transfer secret information directly to the trusted hypervisor in a safe manner. The secret information can then be used by the hypervisor to carry out cryptographic operations allowing it to further communicate, in confidence, with the attestation server. It can also receive, interpret and validate additional encrypted information, utilizing that to augment maintenance of cyber-security in a computer system.

#### 1.5.3 Existing Methodologies Evaluation

In 2016, Microsoft added a similar methodology to Windows 10, called *Device Guard* [41]. Device Guard is a group of features designed to take advantage of hardware-virtualization, SLAT and IOMMU to protect systems against unsigned applications, malware and APTs. Microsoft calls this technology *Virtualization Based Security* (VBS). The technology Microsoft offers is based on Microsoft's own Hyper-V, which is a full blown hypervisor that is integrated into Windows OS.

To take advantage of Hyper-V it must be booted before the Windows OS. Similar to the methodology proposed in this thesis, when Device Guard is employed, the hypervisor verifies code integrity in both Kernel and User mode applications and manages memory access rights based on SLAT. Microsoft provides tools that sign applications (whitelisting) and when Device Guard is active, verifies signatures with components called *CCI* (Configurable Code Integrity) and HVCI (Hypervisor Code Integrity).

Since Hyper-V is a full blown hypervisor, its attack surface is relatively large, which leaves an opening for exploitation attacks [42]. Hyper-V, which is booted before the OS, is not inherently secure and thus cannot be trusted. Therefore, potential attacks on the integrity of Hyper-V may be attempted to circumvent Device Guard. A secure boot, based on TPM, could be employed, however besides the added TPM hardware requirement, TPM has been broken, as mentioned above [19] [20] [21].

Furthermore, since the technology is based on Hyper-V, it is applicable only to systems running Microsoft operating systems.

#### 1.6 Research Contribution

A methodology and system that achieve a strong system-wide protection against execution of a wide array of unauthorized code penetrations is proposed and studied. The research approach is distinguished from previous efforts by the implementation of an *attested* thin-hypervisor, which launches in an existing OS and which extends its security model over existing legacy applications without requiring their modification.

The lean thin-hypervisor proposed provides for an extremely small surface of attack. The attestation procedure described provides a software-only solution that ensures the hypervisor can be trusted and contains safeguarded secret key material.

The unique approach described here allows a system to dynamically shift between protected and unprotected modes of operation. This situation can be appreciated, for example, in a BYOD situation, where enterprise employees can use their own computers for private (unsecure use) without enduring the performance overhead associated with hypervisor protection (see <a href="chap: 4.5.1">chap: 4.5.1</a>), then shifting dynamically into protected mode to run office applications that

warrant extensive security. Applications that execute in protected mode shall be protected and isolated from any malicious code the computer may have contracted. Dynamically shifting into protected mode is based on the capability to activate a thin-hypervisor after an OS already prevails. Securing trust in this situation entails administering a remote attestation procedure to establish a trusted environment in an otherwise untrusted computer system.

The lean thin-hypervisor design is extremely apt to porting to other operating systems. Currently it is operating on Windows, IOS and Linux with ports to ARM/Android underway. Furthermore, since the proposed thin-hypervisor is unrelated to a specific operating system, it may be used as a hosting hypervisor in a nested-hypervisor environment to provide application execution protection for applications running on multiple operating systems on the same computer system.

#### 1.7 Author Contribution

The author is a major team member of the TrulyProtect research team, which was financed by the Finnish agency TEKES and the University of Jyväskylä. The author significantly contributed, together with the other team-members, to the research project in conceiving the ideas and developing the theory and the framework behind setting-up a trusted thin-hypervisor and its remoteattestation for the purpose of securing a computer system against malicious software attacks. The author also substantially contributed to writing the software that implements the proposed methodologies that are studied under this research.

Summaries of the included articles along with the author's contribution to each are detailed in chapter 6.

#### 2 USING A HYPERVISOR TO ENFORCE TRUST

#### 2.1 Hypervisors and Hardware-Assisted Virtualization

A hypervisor, also referred to as a Virtual Machine Monitor (VMM), is software, which may be hardware assisted, to manage multiple virtual machines on a single system. The hypervisor virtualizes the hardware environment in a way that allows several virtual machines, running under its supervision, to operate in parallel over the same physical hardware platform, without obstructing or impeding each other.

Hypervisors have been in use as early as the '60s on IBM mainframe computers [43]. After 2005 Intel and AMD have added hardware support in the form of virtualization extension instructions that are an extension to the x86 instruction set architecture, allowing isolation of multiple operating systems efficiently, thus facilitating the construction of virtual machine monitors (Hypervisors) [44] [45]. Note that previously, construction of virtual machine monitors involved binary instrumentation and required modification in the code of the hosted operating systems.

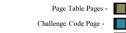

Each virtual machine has the illusion that it is running, unaccompanied, on the entire hardware platform. The hypervisor is referred to as the Host, while the virtual machines are referred to as Guests. Hypervisors are further categorized as: type-1 [46] (or bare metal) and type-2 hypervisors [47].

A type-1 hypervisor executes independently and directly over the system hardware. The OS of the Guests run above the hypervisor, in effect decoupled from the system hardware by the hypervisor.

A type-2 hypervisor executes above a cooperating OS, where Guests run atop the hypervisor. This type of hypervisor uses the cooperating OS as a means to access and manage hardware resources.

In order to support multiple OS guests, a type-1 hypervisor must unobtrusively intercept OS access to hardware resources so it can attend to them itself. The hypervisor can then manage hardware allocations that maintain proper separation between the Guests. The Guest OS is unaware of the hypervisor's intervention, as it experiences a normal hardware access cycle. The only distinction being the elapsed time, since the hypervisor mediation has a time-toll.

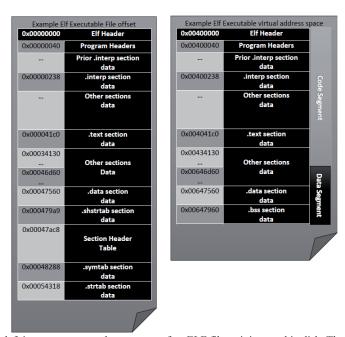

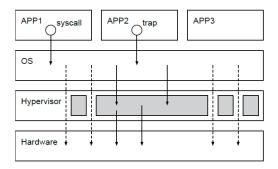

FIGURE 1 depicts a virtualized system featuring a hypervisor that manages two Virtual-Machines (VMs), each running an operating system that manages its user applications. The hypervisor runs at a higher privilege level than the operating system. System calls, traps, exceptions and other interrupts, transfer control from user mode applications to their operating system. The operating systems handle these conditions by requesting services from the underlying hardware. The hypervisor is configured to intercept all those requests and handle them according to its policies.

FIGURE 1 Virtualized system with 2 Virtual-Machines (VM). Each VM is a stack comprised of an OS with applications running over it. Applications utilize the OS by making system calls and Trap intercepts. Each OS believes to be running over the hardware platform, however OS requests from the hardware are intercepted and managed by the hypervisor, which maintains isolation between the VMs.

To intercept all OS hardware access, hypervisors are configured to intercept privileged instructions, memory access, interrupts, exceptions and I/O, which are the OS vehicles for hardware access. Executing an intercepted privileged instruction causes a hypervisor VM\_EXIT. In other words, the Guest VM is exited and the configured hypervisor intercept-routine is executed. When this occurs, the CPU mode changes from Guest-mode to Host-mode.

Guest applications that require hardware resources, execute system calls to request support from their OS. FIGURE 1 depicts this chain-of-execution for a type-1 hypervisor with two Guest stacks. After fulfilling the intercept, the hypervisor indiscernibly returns to the Guest.

While hypervisors were generally designed to serve as virtual machine monitors, type-1 hypervisors, which control the underlying hardware platform, also providing a very good fit to serve as software security facilitators.

Hypervisors have been previously used to secure systems. For example, the Software-Privacy Preserving Platform (SP3) [48] utilizes a hypervisor to maintain isolated memory-pages in protection-domains. Physical pages in the system can be individually encrypted with a symmetric-key, where each domain has an associated set of keys whose pages it is allowed to use. The hypervisor intercepts interrupts and exceptions and uses shadow page-tables to manage decryption and encryption of the appropriate pages when the application shifts between domains. This methodology keeps domain access to protected pages isolated from other domains as well as from the OS. The hypervisor stores the key-database and domain key-associations in its own isolated memory.

#### 2.2 The Thin-Hypervisor

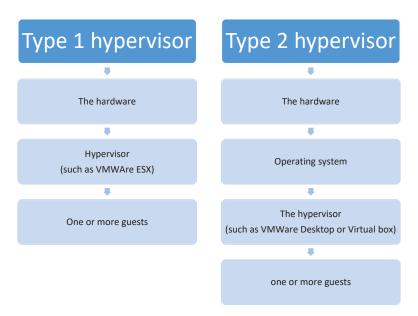

Our research project proposes to use a type-1 hypervisor environment for securing a single Guest stack. Rather than wholly virtualizing the hardware platform, a special breed of hypervisor, called a thin-hypervisor [49] [50], is used. The thin-hypervisor is configured to intercept only a small portion of the system's privileged events. All other privileged instructions are executed without interception, directly, by the OS. The thin-hypervisor only intercepts the set of privileged instructions that allows it to protect an internal secret (such as cryptographic key material) and protect itself from subversion. FIGURE 2 depicts a thin-hypervisor supporting a single Guest stack. The thin-hypervisor does not control most of the OS interaction with the hardware, therefore multiple OSs are not supported. However, system performance is kept at an optimum. Additionally, the thin-hypervisor runs at a higher privilege level than the operating system. System calls, traps, exceptions and other interrupts, transfer control from user mode applications to the operating system. The operating system handles these conditions by requesting service from the underlying hardware. The thin-hypervisor intercepts only a few of those requests, while remaining transparent to all others, which are thus serviced directly by the hardware.

Thin-hypervisors have been previously used for security purposes. For example, TrustVisor [51] is a thin-hypervisor that enables isolated execution of designated portions of an application. TrustVisor is booted securely by making use of a TPM chip and once in operation, it depends on hardware virtualization to isolate portions of memory with Secondary Level Address Translation (SLAT) as well as protect memory from DMA access by physical devices with DEV or IOMMU. TrustVisor utilizes this capability to (i) protect itself; and (ii) extend TPM facilities to a so-called  $\mu$ TPM environment that is used to provide high-speed trusted-computing primitives. These capabilities are further used by

TrustVisor to achieve its ultimate goal of supporting a totally-isolated execution environment for designated self-contained software routines, called PALs (Pieces of Application Code). Software developers designate the portions of their codes that require isolation and group them into appropriate PALs. The developers register the PALs by providing a description of PAL bounds as well as memory regions they need to access. The TrustVisor guarantees that when PALs are called they operate in an isolated memory environment until they are exited.

FIGURE 2 Thin-hypervisor securing a single VM stack. The thin-hypervisor only virtualizes a select subset of the OS's hardware requests. Most OS operations are executed directly by the hardware.

A thin-hypervisor facilitates a secure environment by:

- (a) Setting aside portions of memory that can be accessed only when the CPU is in Host mode

- (b) Storing cryptographic key material in privileged registers, and

- (c) Intercepting privileged instructions that may compromise its protected memory or key material

A thin-hypervisor is also less susceptible to being hacked as a result of vulnerabilities, since its code and complexity are greatly reduced, as compared to a full-blown hypervisor. This serves to significantly reduce the threat surface that needs to be protected.

Once this environment is correctly setup and configured, the thinhypervisor can be utilized to carry out specific operations, which may include use of the internally stored key material, in a protected region of memory. As a result of the tightly configured intercepts and absolute host control of select memory regions, this activity can be guaranteed to protect both the secret key material and the operations' results.

A correctly configured and active thin-hypervisor can effectively protect the secret key-material, after it is safely stored in privileged registers. However, the procedure by-which the secret material gets stored while the thin-hypervisor is being setup – is delicate business, since an adversary can potentially grab the secret at that point. An additional question, requiring an answer, is where the secret is kept while the thin-hypervisor is not active?

The approach to solving these issues is comprised of the following principles:

- 1. While the thin-hypervisor is not active, the secret key material shall not be stored anywhere in the system

- 2. When setting up a thin-hypervisor, an external system shall be used to verify that the thin-hypervisor has control over the underlying hardware

- 3. The same external system that verifies the thin-hypervisor shall provide the secret key-material

The first principle is important to rule out the possibility of keeping secret material under the cover of obfuscation, which is known to be ultimately vulnerable. The second and third principles require maintaining a remote attestation server system and equipping it with the facilities to verify that a thin-hypervisor has been properly setup and configured on a remote system, such that a trusted environment is primed and can accept secret material, as well as keep it secret.

#### 2.3 Attestation of a Remote Hypervisor Activation

Hypervisors can be nested. In other words, a hypervisor's Guest can itself be a virtualized system embodying a VMM (Host) and VMs (Guests) [52]. In order to support such a configuration the outermost surrounding hypervisor needs to specifically support nested-virtualization.

We introduce the concept of a *Root-Hypervisor*: A Root-Hypervisor is the distinct hypervisor that has the ultimate control over the hardware platform. A Root-Hypervisor does not have to support nested-virtualization. However, in a nested virtualization environment the surrounding hypervisor, which supports and manages nesting is invariably the Root-Hypervisor.

Hypervisor activation can be part of the system boot process or can occur *after* an OS is already active. This is achieved by capturing the OS instance, taking (virtualization) control of the system and instantiating the OS instance as a Guest (VM). Such a rootkit driver, dubbed "*Blue-Pill*" was suggested in 2006 by Joana Rutkowska [53] and independently by King and Chen [54].

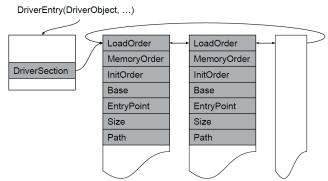

Configuring and installing a hypervisor can only occur while the system is in Kernel-mode, since hypervisor instructions are all privileged instructions. Therefore, when launching a "Blue-Pill" style hypervisor, under the supervision of an operating system, the hypervisor configuration and installation functions must be implemented in a kernel-mode system software driver. We call this the *HDriver* (Hypervisor-Driver). The target system must have the HDriver installed and registered in order to successfully launch the hypervisor installation.

Once a Root-Hypervisor has taken control of the system, by becoming a VMM host, it is capable of intercepting all further hardware events. This includes the aforementioned capability to manage and support the upbringing of a nested-hypervisor by one of its Guest VMs. Furthermore, the Root-Hypervisor can take measures to conceal its existence. For example, by falsifying results of intercepted instructions that probe the hardware. This type of behavior has been suggested as an approach for hackers implementing hypervisor-based malware [55] [56].

It is self-evident that the Root-Hypervisor needs to be the **first** hypervisor to take control of the system. Being the first hypervisor to virtualize the system secures the opportunity to intercept hardware events as well as fully control the intercept activity of nested hypervisors.

When attempting to use a hypervisor as the base foundation for enforcing trust in a computer system it is unequivocally essential to determine that the hypervisor is a *Root-Hypervisor*. In other words that it is the first hypervisor to virtualize the system, and thus has ultimate control of the hardware platform. Given the disingenuous capabilities of a hardware-virtualization based hypervisor, this task as not as simple as may initially appear [57] [58].

However, verifying that the hypervisor is a Root-Hypervisor is not the only concern in establishing trustworthiness. Granted, once the hypervisor is in control and validated as a Root-Hypervisor, it may be safe to assume that it can be utilized to enforce trust, as well as protect itself, as discussed in the paragraph below. However, during the process of establishing the hypervisor's control, even assuming it is the first hypervisor, it is critically exposed to subversion. The main concerns are the possibility of a malicious software making changes to the hypervisor's code or data-structures just before it takes control. These concerns are especially acute when the hypervisor is launched while an OS is already prevailing, since the potential of its being infected by malicious code is eminent. Furthermore, modern computer CPUs consist of more than a single processing unit, organized in a hierarchy of cores and logical processors. With multiple cores the system can execute several programs in parallel. This imposes additional verification requirements, since it is potentially possible for malicious code running on one core to undermine the process of establishing the hypervisor on another. Moreover, the system can be regarded as trustworthy only if a root-hypervisor is successfully instantiated and verified on all the existing cores.

Attestation [59] [60] is the collective effort of verifying and validating that the hypervisor is a root-hypervisor, properly installed on all cores, that has not been subverted in any way. Namely it establishes a *trusted platform* in a target computer system.

One of the main instruments to facilitate attestation is *time-measurements*. The reason for this is the execution overhead associated with virtualization intercepts. For example, an attestation procedure may measure the time it takes to complete a pre-known procedure and attempt to determine whether intercepts occurred and accordingly consumed time. However, timing measurements cannot be conducted by the system being attested, since requests to fetch time readings from the hardware can be intercepted and the results falsified. Hence, an external system must be involved in the attestation process. We use an *Attestation Server* for this purpose and perform a *Remote-Attestation Procedure*. The attestation server communicates with the attestation target, sends it a *challenge* in the form of executable instructions and measures the turn-around response time. In this case, the time measurement can be considered objective.

#### 2.4 Protecting a Thin-Hypervisor that Enforces Trust

We assume at this point that a thin-hypervisor is brought up on a computer system and it is successfully attested by an attestation-server, therefore it can be trusted. In the next chapter we will explain and demonstrate that following a successful attestation procedure we can assume the following:

- The hypervisor is a Root-hypervisor, i.e., it is the first hypervisor to be launched in the computer system and it has control of the underlying hardware

- The hypervisor code contents are verified and authenticated, i.e., instructions that will execute in host mode have not been subverted, therefore the hypervisor can be trusted to perform as intended

- The hypervisor contains secret material, received in confidence from the attestation-server, during the attestation procedure. The secret material is known only to the hypervisor and the attestation-server

A significant part of the hypervisor configuration and routines must be dedicated to enforcing and maintaining trust *after* the attestation has validated the initial conditions of trust. To accommodate, the hypervisor's surface of attack must be considered and appropriate means need to be deployed to provide ample resistance. The following major aspects of hypervisor trust maintenance are reviewed, as examples:

#### 2.4.1 Secret Material Storage

The hypervisor receives secret material in confidence from the attestation-server. The secret material is a basis for cryptographic operations, such as decryption or signing, which the hypervisor carries out as part of the general security-scheme implemented by the hypervisor. Naturally, this secret material must be kept out of reach and is a potential target for an adversary wishing to subvert the hypervisor functions. To overcome this, the hypervisor stores the secret information in privileged registers, as well as configures VM exit intercepts on access attempts to the privileged registers. See section 25.1.3 in [44]. Any attempt to access these registers will be intercepted by the hypervisor, which will either ignore the access request or report an invalid result.

#### 2.4.2 Protecting Hypervisor Configuration-Structures

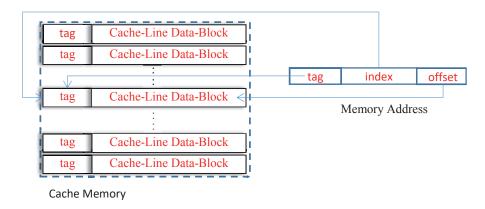

Hypervisor configurations are stored in dedicated data-structures. For example, VMCS in Intel, section 24.1 [44] and VMCB in AMD, section 15.5.1 [61]. The contents of these repositories must be vigorously defended from illicit access. Otherwise an adversary might make changes that will eventually subvert the hypervisor. For example, she may replace the address setting of the intercept handler, and thus, when a VM exit intercept occurs, the adversary's intercept routine shall be activated instead of the intended one. To subjugate this threat, the hypervisor takes advantage of a mechanism called Second Level Address Translation (SLAT). See Intel EPT chapter 28 of [44] and AMD RVI chapter 15.25 [61]. SLAT is discussed later in section 4.1. At this point we only mention that SLAT allows a hypervisor complete control over memory access-rights. Subject to this, the hypervisor configures the SLAT to disallow any access to the memory pages that contain it configurations. In effect, this memory does not exist outside host mode and therefore cannot be accessed.

#### 2.4.3 Using Intel VT-d and AMD-Vi (IOMMU)

While SLAT provides an immaculate solution to protect against memory access performed by software running on one of the core processors, I/O device DMA transfers provide an alternate route to access memory. Virtual to physical address translation during CPU memory transfers is managed by the MMU (Memory Management Unit), which implements SLAT when hardware virtualization prevails. On the other hand, I/O device DMA allows devices to access memory directly. An adversary may potentially attempt to affect critical memory sections protected by the hypervisor with SLAT, using DMA or RDMA (Remote DMA), thus subverting the hypervisor and penetrating the system. Fortunately, Intel and AMD have implemented solutions for this issue to enhance hypervisor performance. The motivation for this was to allow a hypervisor means to configure I/O device DMA access that ensures VM separation without resorting to hypervisor intercepts on each I/O access. Intel have added the IOMMU and VT-d technology, called "Virtualization"

Technology for Directed I/O" [62] and AMD have added AMD-Vi technology "AMD I/O Virtualization Technology (IOMMU) Specification" [63]. AMD-Vi and Intel VT-d technology provide facilities to configure the IOMMU to remap DMA addressing. The configuration is used to map separate VM devices to individual and isolated memory domains. Each VM can then access only its own memory domain and is blocked from other VM domains. To avert potential subversion by accessing memory, the thin-hypervisor configures the IOMMU to remap the (single) VM's I/O DMA access to a memory domain that excludes the same memory pages protected by the SLAT. This procedure ensures that critical pages, whose access is allowed only by the hypervisor, are protected both from memory access as well as DMA and RDMA access. In effect, being completely invisible to the outside world.

#### 2.4.4 Secure AES Cryptography

Based on the availability of secret material stored inside the hypervisor and protected in privileged registers, the hypervisor may perform cryptographic operations as part of the general security-scheme. An adversary that is aware of this, may attempt to attain the AES key using side-channel attacks [64] [65]. To avoid this threat the hypervisor uses a hardware implementation of AES, available on modern processors, such as AES-NI (AES New-Instructions) [66]. Furthermore, the implementation of AES cryptography is managed entirely in CPU registers, as opposed to using memory buffers for intermediate results. This combination reduces vulnerability to potential side-channel attacks to virtually non-existent [67] [68].

#### 2.4.5 Intercepting Critical Instructions

The thin-hypervisor must also protect its existence. Since malicious code may also penetrate the system and achieve kernel-level execution mode, it is imperative to intercept all privileged instructions that may obstruct the hypervisor's presence. Thus, for example, the *VMXOFF* instruction, which causes the system to exit Virtualization mode must be intercepted and ignored. Similarly, *VMPTRLD*, *VMPTRST*, *VMCLEAR*, *VMWRITE* and *VMREAD* instructions, which access the hypervisor configuration structures must be intercepted and ignored as well.

## 3 REMOTE SOFTWARE ATTESTATION METHODOLOGY

#### 3.1 Previous Work

Pioneer [69] is a software-only component designed to provide execution of a remotely authenticated executable on an untrusted and possibly compromised legacy host system. Pioneer is composed of a dispatcher system that is used to manage a challenge-response protocol with the untrusted platform, where an authenticated executable is to be run. The methodology of Pioneer is based on a verification utility, which first establishes itself as a root of trust, by executing code that both checksums itself and verifies that it is running. The verification utility is randomized by receiving a challenge seed from the dispatcher. Once trusted, the verification utility proceeds to authenticate the executable in question. Pioneer is based on two assumptions on the untrusted platform:

- (a) It has a single logical processor

- (b) It does not contain a virtualization extension