# University of Jyväskylä Faculty of Mathematics and Sciences Department of Physics Nanoscience Center

# Andrii Torgovkin

# High-frequency filtering for low-temperature thermal transport studies in nanostructures

Supervisor: Prof. Ilari Maasilta

Jyväskylä 2012

#### Abstract

Filtering of external unwanted RF-noise and thermal noise generated at the high-temperature parts of the measuring circuit is essential for successful measurements of thermal transport of nanostructures at low temperatures. This is because of thermal decoupling of the systems, i.e. the extreme weakness of thermal conduction at sub-Kelvin temperatures, leading easily to overheating even with excess power in sub pW range. We have started to improve the noise filtering in our cryogenic dilution refrigerators, which can reach a base temperature of  $\sim 50$  mK. The miniature low-pass filters were made from special RF sealing compound Eccosorb CR124, stainless steel powder of grain size 50  $\mu m$  and a typical low-temperature epoxy (Stycast). Measured cut-off frequency is at 1 MHz, low enough to cut most of the radiated RF power.

# Contents

| 1. Introduction                                             | 4  |

|-------------------------------------------------------------|----|

| 1.1 Problem statement                                       |    |

| 1.2 Noise heating.                                          |    |

| 1.3 Johnson noise                                           |    |

| 2. Cryogenic setup.                                         |    |

| 2.1 Refrigeration                                           |    |

| 2.1.1 Equipment                                             |    |

| 2.1.2 Wiring of the refrigerator.                           |    |

| 2.1.2 withing of the refrigeration.                         |    |

| 2.2.1 Problem definition                                    |    |

| 2.2.2 Filters overview                                      |    |

| 2.2.3 Filter fabrication                                    |    |

| 2.3 Sample stage                                            |    |

| 2.4 Evaluation of high frequency filters.                   |    |

| 2.5 Discussion about filter characteristics                 |    |

|                                                             |    |

| 3. SINIS thermometer sample                                 | 27 |

| 3.1 Sample overview                                         | 27 |

| 3.2 Sample fabrication steps.                               |    |

| 3.2.1 Substrate cutting.                                    | 29 |

| 3.2.2 Substrate cleaning.                                   | 29 |

| 3.2.3 Substrate oxidizing.                                  |    |

| 3.2.4 Sample chip preparation                               | 29 |

| 3.2.5 Back gate formation                                   |    |

| 3.2.6 Insulating layer formation                            |    |

| 3.2.7 SINIS junction design and fabrication.                |    |

| 3.2.8 Exposure                                              |    |

| 3.2.9 Development                                           |    |

| 3.2.10 Metal deposition                                     |    |

| 3.3 SINIS junction theoretical background.                  |    |

| 3.4 Sample characterization                                 |    |

| 3.5 Discussion about the sample data.                       |    |

| 3.5.1 Experimental data discussion                          |    |

| 3.5.2 The data description by modified model                |    |

| 3.5.3 The comparison of experimental and theoretical curves | 55 |

| 4. Conclusions                                              | 62 |

| References:                                                 | 63 |

#### 1. Introduction

#### 1.1 Problem statement

Since superconductivity was discovered by Kamerlingh Onnes in 1911, very many devices, of both practical and scientific interest, had been utilizing this phenomenon. Superconducting devices usually require extreme cooling, in many cases below boiling point of helium. It is also evident that the refrigeration ability of the cooling device decreases with the decrease of temperature. For example, <sup>3</sup>He<sup>4</sup>He dilution refrigerators used in this work have cooling power only several microwatts at temperatures below 0.1K and several tens of nanowatts below 0.050K. As one wants to maintain reasonably short cooling times, experimental setups are usually done with small samples.

Many cryogenic experiments need precise temperature measurements of micro- and nano-scale objects. There are variety of thermometers available to physicists working in the sub-K region. But already long ago the scientific community has turned its sight to the small-scale devices, in particular to nanoscale circuits, and to devices with reduced dimensions which have a large thermal response. The superconducting tunneling junction is one example of this kind of device. In this work, normal metal-insulator-superconductor tunnel junctions (NIS) are considered.

NIS junctions have been intensely studied since 1960s [1, 2]. Both fundamental [3, 4] and applied research has been carried out [5, 6]. Nowadays two main properties of NIS junctions are utilized in research projects of nano- and mesoscopic electronic devices. The first one is the strong dependence of NIS current-voltage characteristic on its electron temperature. It facilitates the development of electron temperature sensors for microbolometers [9] and nanodimensional structures [8]. The second property is cooling of metallic structures by means of electron tunneling. Both electrons and phonons cooling with NIS junctions have been demonstrated [9]. The physical mechanism of the cooling is based on a selective tunneling of hot electrons through the insulating barrier. When the junction is biased at voltages  $V \le \Delta/e$  ( $\Delta$  stands for superconductor energy gap), only the particles with energies  $E > \Delta$  can tunnel from the normal metal into the superconductor, since the states within the superconducting gap are forbidden. The on-chip cooling is essential for development of ultra-sensitive radiation sensors [9], qubits, etc.

In practice, NIS junctions are used in series to make the device symmetrical. NIS junctions are very miniature devices themselves, usually with dimensions of 100 to 500nm and several microns of supporting wires with typical thicknesses of several tens of nanometers. This yields in a very small mass of the device and thus a very small heat capacity. Assuming a junction size of 500nm by 500nm made of aluminium, aluminium oxide and copper, the mass of SINIS junction (which is simply a doubled NIS junction) can be estimated as 1.5 picograms, including 10 micrometers long supply leads. At room temperature the specific heat of copper is 0.385 J/(g·K), and thus the heat capacity of considered junction elements is about 0.57·10<sup>-12</sup> J/K. At low temperatures the specific heat of copper is reduced almost in 4000 times [10] and so does the heat capacity of SINIS. Thus, even an amount of energy as small as 10 picojoules accidentally applied to the cooled setup may completely ruin the experiment by increasing the temperture by 100mK.

#### 1.2 Noise heating.

In low temperature experiments SINIS junctions are usually biased with currents up to several nanoamperes, and with a typical tunneling resistances of  $10k\Omega$ , this leads to a very small ohmic heating of the junctions. However, in real laboratory the measurement process is not ideal and biasing signal may

also carry noise of different components, which may deliver undesired power to the junction, heating it up.

The most significant contributors to the noise picture of the typical low-temperature experiment are: externally generated noise, flicker noise, shot noise and thermal (Johnson) noise [11].

External noise may consist of: 50Hz component together with its higher harmonics, or noise coming from digital electronic circuits involved in the experiment. External interference, such as communication radio frequency signals or an electromagnetic field of the power lines are usually avoided by placing the experimental setup inside an electromagnetically shielded room, and electrically decoupling it from the computers.

Flicker noise, which is also called 1/f noise, shows mostly at lower frequencies, as its power spectral density is inversely dependent on the frequency. It originates from different phenomena related to direct current. This type of noise, if coming from external circuit, together with external interference, can be eliminated by using proper low pass filters, installed in cryostat. The 1/f noise intrinsic to the tunnel junction, cannot be eliminated.

Shot noise is a type of electronic noise that may be dominant when the finite number of electrons in an electronic circuit is sufficiently small so that uncertainties due to the Poisson distribution, which describes the occurrence of independent random events, are of significance. In tunnel junctions, the magnitude of shot noise increases according to the square root of the expected number of electrons, passing through circuit. However, in ordinary metallic wires shot noise is almost completely cancelled due to anti-correlation between the motion of individual electrons, acting on each other through the coulomb force.

#### 1.3 Johnson noise

Johnson-Nyquist noise (thermal noise) is the electronic noise generated by statistical fluctuations of electric charge carriers (usually electrons) inside an electrical conductor at equilibrium, which happens regardless of any applied voltage.

The mean-square potential fluctuation over the conductor is proportional to the electrical resistance and the absolute temperature of the conductor [12, 13]. It is independent of the size, shape or material of the conductor. It is independent of the electrical circuitry as well. Its apparent magnitude depends on the electrical characteristics of the measuring system as well as on those of the conductor itself [12].

The magnitude of the electrical noise is usually defined by the spectral density S(v). Nyqist showed [13] using equipartition law of thermodynamics that the spectral density of the voltagenoise S(v) across the resistor R in the general case is

$$S_{V}(v) = 4R \left( \frac{hv}{\exp(\frac{hv}{k_{B}T}) - 1} + \frac{1}{2}hv \right), (1.1)$$

here h is Plank's constant,  $k_B$  – Boltzman constant and T is temperature. This model takes into account the fundamental quantum nature of the noise, and the zero-point oscillations term hv/2. However, the quantum zero-point term does not carry any power. It can be explained by the fact that the opposite power is transferred from the termination resistor, even at T=0. Thus, quantum zero-point term only sets the increase of fluctuations if high enough bandwidth is considered. In this work we consider the noise power, which may influence the behavior of the tunnel junction, and not the fluctuations of the voltage readings during the measurement process. The voltage spectral density for the radiated power is then given by:

$$S(v) = 4R \left( \frac{hv}{\exp(\frac{hv}{k_B T}) - 1} \right). (1.2)$$

When frequency is low ( $\nu \ll \frac{k_B T}{h}$ ) the spectral density becomes

$$S(v) \approx 4Rk_BT \cdot (1.3)$$

The noise power W delivered by a conductor through a transmission line to a resistive termination  $R_0$  is

$$W = \frac{\left\langle \delta V^2 \right\rangle}{R_0}, (1.4)$$

here  $\langle \delta V^2 \rangle$  is squared averaged voltage deviation generated by charge thermal agitations. It can be calculated using the voltage spectral density:

$$\langle \delta V^2 \rangle = \int_{0}^{\infty} S_{V}(v) dv$$

. (1.5)

Taking into account that the main task of this work is to construct low-pass filtering, we can consider finite bandwidth of noise power while integrating (1.5).

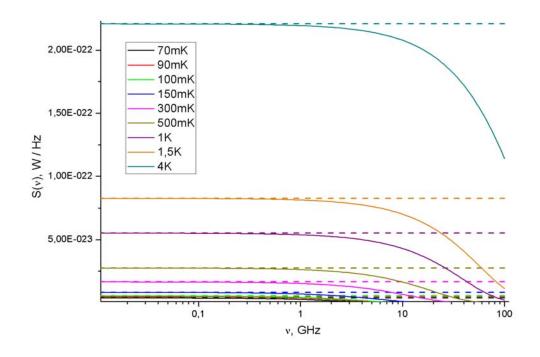

Fig 1.1 represents calculated power spectral density of the Johnson-Nyquist noise at several temperatures as a function of noise bandwidth. Dashed lines give the low frequency limit (1.3), solid lines represents the full formula (1.2). At the low frequency limit, the curves for the noise spectral density are flat. Therefore, the Johnson noise is typically considered to be white noise, as most measurement bandwidths are less than the crossover to quantum noise.

a)

**Figure 1.1.** Power spectral density of the Johnson noise at several temperatures. a) Linear scale b) Log scale

In the most general case, the circuit is characterized by a complex impedance  $Z(\nu)$  that has to be accounted properly instead of  $R_0$  in equation (1.4) [12, 14].

For the low frequency limit (

$$\nu \ll \frac{k_B T}{h}$$

) the resistor dissipated power is

$$W = 4k_B T \Delta \nu . (1.6)$$

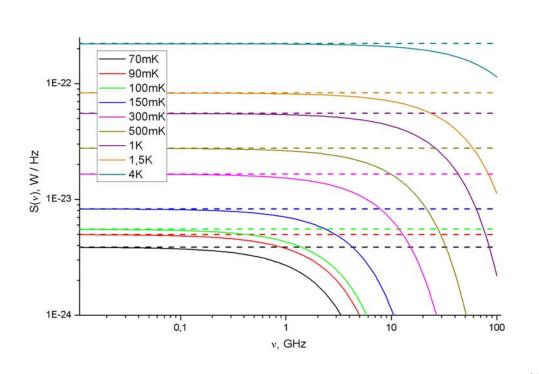

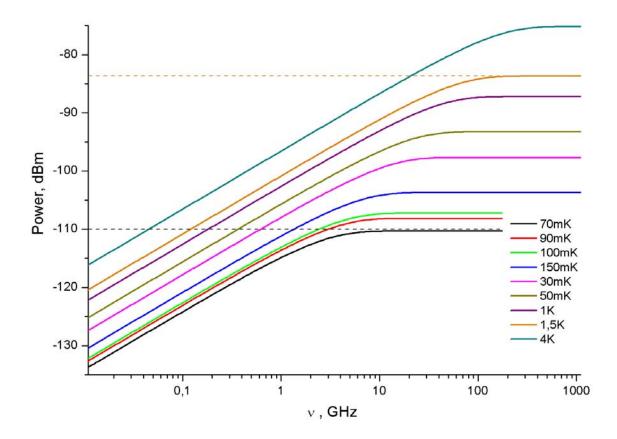

In general case the equation (1.2) sets the power. Fig 1.2 shows the noise power, delivered to a matched load as function of frequency bandwidth  $\Delta \nu$  at different temperatures. Here, the power is measured in dBm units, which can be converted to SI (watts) using following expression:

$$W = 10^{(x-30)/10}$$

, (1.7)

where W is expressed in watts and x is, expressed in dBm.

**Figure 1.2.** The Johnson noise power as function of frequency bandwidth.

Taking into account the fundamental thermodynamical nature of Johnson noise, one should realize that it is impossible to eliminate this noise at given temperature. When the low temperature experiment is considered, there are sources of thermal noise of different temperatures from different stages of the cryostat. It can be seen from Fig 1.2 that a matched resistor at 4K generates more than 30pW (-75 dBm) of noise power and 4pW (-84 dBm) at 1.5K. This power can be transferred further to the circuit elements and make the electron gas in metals to reach possibly the same temperature as the noise has. When a tunnel junction is a part of the circuit, this power can cause an extra increase of its

electron temperature that is often undesirable. This heating leads to changes in tunnel junction electrical behavior, making it impossible to use as a thermometer at the lowest temperatures. Other possible consequence of the noise heating may be seen as the so called leakage current in the sub-gap region of the superconductor of tunnel junction. The broadening of the density of states is often introduced in tunnel junction phenomenological model because of that (see section 3.3).

One possible solution to this problem is to install filtering directly at the lowest temperature stage of the cryostat. According to Figures 1 and 2 one can see that the noise power increases if high frequencies can be transmitted. Filtering at frequencies over several tens of GHz is challenging, as regular filtering elements, constructed with passive electrical components (resistors, capacitors and inductors), offer only very limited attenuation at high frequencies. Very special filtering techniques have to be involved. Miniature cryogenic metal powder filters are considered in this work.

Another way of filtering is suggested in references [15], [16] and in particular in ref. [17]. There authors used RC filters with capacitive and resistive elements fabricated directly on the chip surface. This useful approach is also implemented in the present work.

# 2. Cryogenic setup.

### 2.1 Refrigeration

#### 2.1.1 Equipment

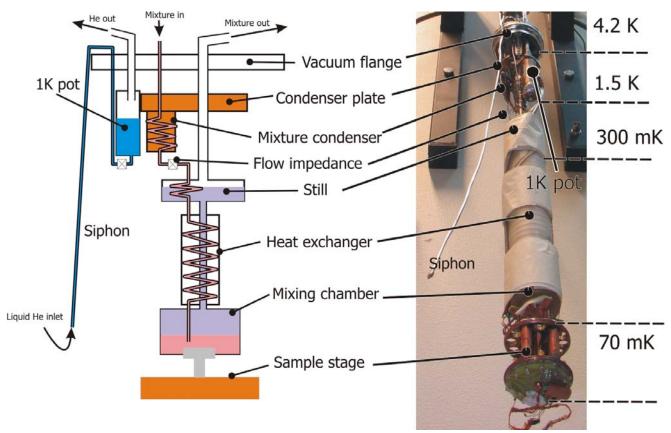

Low-temperature experiments mentioned in this thesis were performed with a home-made plastic dilution refrigerator (model PDR-50) [6, 18, 19]. First, the sample was mounted on the sample stage, which was attached to the refrigerator. After placing the vacuum can, sealing it and checking the vacuum leaks the cryostat was precooled with liquid nitrogen to 77K, maintaining coarse vacuum inside the jacket. At 77K the 0.5mbar of <sup>3</sup>He were introduced to the environment inside the vacuum jacket. Next precooling with liquid Helium to 4.2K was done. As <sup>3</sup>He has lower boiling point than <sup>4</sup>He, at 4.2K it stays in gaseous form and is easily pumped away before further cooling. After this the dilution refrigerator was driven to achieve base temperature of 70mK.

The dilution refrigerator is a closed-cycle unit, allowing continuous cooling operation. The principals of dilution refrigeration can be found in many low-temperature physics books such as [11, 20, 21]. The unusual phase separation between <sup>3</sup>He and <sup>4</sup>He at low temperatures is the quantum physical effect that allows performance of dilution cooling (Fig 2.1) [20].

**Figure 2.1**. Phase diagram of liquid -<sup>3</sup>He-<sup>4</sup>He mixtures at saturated vapor pressure. The figure is taken from [20].

The schematic picture of the dilution refrigerator used in this work is shown in Fig 2.2. The dilution refrigerator has two thermally decoupled chambers, which are connected by means of input/output tubes. The upper chamber is called still and the lower one is called mixing chamber. The sample stage is thermally anchored within the mixing chamber. Another key component of the dilution refrigerator is the heat exchanger. The heat exchange occurs between the liquid helium that passes along the input tube and the liquid passing along output tube. The still, mixing chamber and heat exchanger can be made of metal as well as being plastic. Plastic heat exchanger, for example, has lower thermal boundary resistance than metallic one [20]. So less heat is reflected from the walls and lower temperatures can be reached. The tubular heat exchanger comprises a rod having one spiral groove from one end to the other. The groove accommodates plastic capillary (input channel). The output tube of the heat exchanger, which is used for the transportation of diluted <sup>3</sup>He away from mixing chamber, is located exterior to the input tube. The diluted <sup>3</sup>He is absorbing heat from <sup>3</sup>He-rich phase and prevents heat flow from the higher temperature stages. More information about plastic heat exchanger can be found in [22].

Figure 2.2. The schematic picture of the plastic dilution refrigerator Nanoway PDR50.

Circulation of <sup>3</sup>He is achieved by pumping the system at room temperature. Room temperature <sup>3</sup>He gas is precooled by the 4.2 K <sup>4</sup>He bath. Then the gas goes towards a <sup>4</sup>He evaporator called the pot. It is condensed there at 1.5K by forced pumping of <sup>4</sup>He from the bath. After that it has to go through main flow impedance, where sufficient pressure is achieved, so that liquefied <sup>3</sup>He must enter a heat exchanger, which is in the thermal contact with the still at 0.7K. After that, the liquid enters secondary flow impedance and passes to the next heat exchanger, where it is cooled by means of dilute phase that goes away from mixing chamber, as it was discussed already above. After being cooled there, the liquid <sup>3</sup>He enters finally the mixing chamber.

Initially the dilution refrigerator contains homogeneous mixture of <sup>3</sup>He and <sup>4</sup>He at 1.5-2K. At these temperatures, the mixture is homogeneous regardless of the <sup>3</sup>He/<sup>4</sup>He concentration ratio. The liquid fills the input tube, the mixing chamber, the output tube and part of the still. The low pressure gas is pumped from the still, in equilibrium with the free surface of the liquid, and is compressed at the room temperature pump. A low impedance pumping line extends from the still to an external pumping system and further to the output line to form the closed-cycle pumping circuit. As soon as gas circulation starts, the temperature of the liquid drops. Below temperatures of 0.87 K the two liquid phases finally separate spontaneously to a normal fluid phase rich in <sup>3</sup>He on top of a superfluid phase rich in <sup>4</sup>He. The phase richer in <sup>3</sup>He has smaller density and floats on the top of the <sup>3</sup>He dilute phase and is pumped out and recondensed, filling the output tube and still. Since the vapor pressure of <sup>4</sup>He is lower than vapor pressure of <sup>3</sup>He, soon only <sup>3</sup>He is circulating and the temperature of the still drops to ~0.3K. But at this temperature the pressure of <sup>3</sup>He becomes very small and circulation nearly stops (being activated only by the heat leak from exterior to the refrigerator) and to cool further, external heat must be applied to the still to maintain the circulation.

The equilibrium concentration of <sup>4</sup>He diluted in <sup>3</sup>He is essentially zero while <sup>3</sup>He diluted in <sup>4</sup>He reaches 6.5% even at zero temperature [20]. In the mixing chamber the concentrated <sup>3</sup>He is in the equilibrium with diluted <sup>3</sup>He. Now if one tries to decrease the limiting concentration of <sup>3</sup>He in <sup>4</sup>He at fixed temperature by pumping the chamber, pure <sup>3</sup>He will cross the boundary and reestablish the equilibrium concentration. This process requires energy so heat will be absorbed and the temperature of the chamber together with its content will be lowered. To maximize the evaporation rate of <sup>3</sup>He, a resistive heater of the still is used. The largest cooling power is achieved when the mixing chamber temperature is very close to the temperature of concentrated phase entering the mixing chamber. For this purpose sometimes very large area heat exchangers are used, namely sintered silver plates.

#### 2.1.2 Wiring of the refrigerator.

The refrigerator used in this thesis has eight measurement lines and seven technological ones. Measurement lines are filtered at several stages. Starting from room temperature to 4.2K all lines are made of manganin wires. Prior to entering the vacuum jacket they are connected to LC-filters (cut-off frequency of 250 kHz). From 4.2K to the 1K pot measurement lines enter a solder joint in the vacuum jacket flange as Thermocoax cables, which additionally filter the high frequencies. Technological lines are coming to the 1K pot as manganin wires through an epoxy feed through. At the 1K pot, the measurement lines enter a microstrip filtering box, where signals are passed through conducting meander on a thin film, surrounded by metal powder - epoxy compound. From 1K pot all lines continue as twisted pairs of high resistance manganin wires to the sample stage, where special high-frequency filters are installed (see section 2.3). Manganin wires are used because of low electrical and thus low thermal conductivity. However, the use of superconducting wires may be also considered. Twisted pairs of manganin wires are wound around the plastic heat exchanger to cool efficiently, assuring that at the lowest temperature end of the cryostat all lines do not introduce unnecessary heat load to the refrigerator.

Temperature of the sample stage is measured with a Ge resistance thermometer GR-200A-3 from Lake Shore Cryotronics, whose resistance is read by a Picowatt AVS-47 resistance bridge. The temperature of the sample stage could be set to required value with the use of resistive heating at the low-temperature end of the cryostat. One 1 k $\Omega$  resistor was installed at the sample stage. The power supplied to the resistor to maintain the constant temperature was controlled by PID controller, implemented in the measurement software.

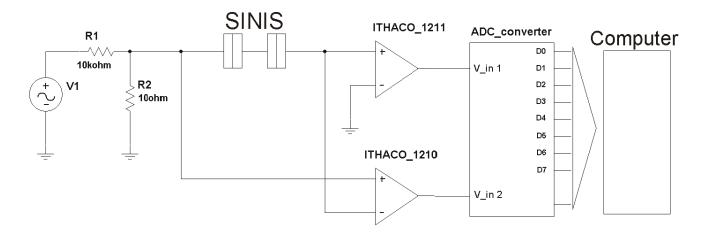

During the measurements, the refrigerator and measurement electronics were placed inside of the electromagnetically shielded room. Measured signals were amplified by room temperature Ithaco Low Noise (1201/1211) voltage and current preamplifiers, and their output was read by an analog to digital converter and transferred to the computer by an optical fiber, to avoid electrical contact between the computer and the measurement electronics. The data acquisition electronic board was read through the GPIB interface by specially developed program in LabView software environment.

#### 2.2 Filters.

#### 2.2.1 Problem definition.

The properly designed cryogenic experiment has to employ several kinds of filtering units. The reason for that is the fact that there is no filter that can achieve suitable attenuation over wide range of frequencies.

Although anchoring the lines to heat sinks reduces the noise they generate, the lines themselves are the things that should be always remembered while designing low temperature filtering. The noise coming from parts at higher temperature can be handled in principle with reflective-type filters. However, reflective-type filters are not adequate, because their performance is very sensitive to impedance

mismatches in the rest of the line, which causes spurious transmission resonances. Therefore, one must typically choose dissipative type filters [23].

It is necessary to filter out the most of the Johnson noise that comes from the hot parts of the cryostat in the form of voltage noise through the measurement lines.

The last filtering stage must be installed at the lowest temperature stage, directly before the sample mounting. This is needed to ensure that the sample will not be exposed to the voltage noise of the filter itself, whose effective electron temperature is mostly higher than phonon temperature of the sample.

In this work in our dilution refrigeration setup the last stage, where the wiring is thermally anchored is the 1.5K stage. Thus, an estimation for the unwanted noise power coming to the sample is 4pW (-83dBm) with the full noise spectrum (see Fig 1.2). The cumulative power spectrum depicted in Fig 1.2 also indicates that the most of the noise power comes in a frequency band starting at  $\sim 100 MHz$ . Frequencies lower than 100MHz are not important because the thermal noise of sample stage wiring itself at the lowest temperature (for instance, 70mK) is producing the same power in the full frequency range as the 1.5K wire noise low-pass filtered at 100MHz (-110dBm). The estimation of the highest noise power that may reach the sample is difficult, and thus we often use 4K thermal noise as an upper limit.

Thus, in order to fulfill good conditions for lowering the electron temperature one has to manufacture high-frequency filters with very high attenuation for the desired frequency range (tens of Gigahertz).

Another function of filters is to conduct away the heat generated from dissipated microwaves. Filters have to be connected to the thermal bath with low enough thermal impedance. This may be achieved with increasing amount of thermo-conducting material. Also one should take into account the finite cooling power of the cryogenic refrigerator, as well as space and mass limits for the lowest temperature stage of the assembly. Thus, a compromise must be found between high thermal conductance and space limitations.

Summarizing, our first task was to manufacture a set of cryogenic low pass filters, effective above 100MHz, having attenuation of at least 60dB and being compact and simple.

There are various ways to solve this problem. Several common solutions are discussed below.

#### 2.2.2 Filters overview.

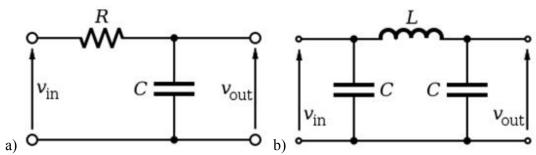

One obvious way to construct filters is to use RC , RL or RLC – filters. However, these designs do not have satisfactory attenuation over several GHz. Below we review and compare different types of filters.

#### RC filter.

Each measurement line can be equipped with a resistor and a capacitor (see Fig 2.3 a). This installation is very compact. A properly chosen resistor can change its resistance only a few percent upon cooldown. However, the capacitance can decrease significantly due to the temperature dependence of the dielectric constant in the capacitors [23, 24].

#### RLC filter.

An inductance can be added to the previous filter in series with the resistor to get more attenuation. This filter has the same advantages and disadvantages as the RC-filter.

On-chip version of RLC filter fabricated by means of optical lithography was presented in [23]. The filtering element is a distributed RLC meander line. The goal of this element was  $\sim$  -80dB at tenths of GHz measured at room temperature [23]. However, these filters are difficult to handle and may not withstand thermal cycling.

#### LC filter.

Since there are no resistive components, attenuation is almost zero up to the filter cutoff frequency. This approach includes also Pi-filters, which have two capacitors (see Fig. 2.3 b) and offers at least 30dB per decade attenuation [23].

**Figure 2.3**. Schematis of the simple electronic filters. a)RC low-pass filter b) LC Pi-filter The figure is taken from [16].

#### THERMOCOAX.

The Thermocoax® was originally developed as a vacuum compatible heater cable but was found to be highly suitable for filtering in cryogenic applications [25]. It shows the typical square-root dependence skin effect without sharp cut-off regions [24, 25].

The center conductor is made from nickel/chrome and the outer conductor is stainless steel. The difficulty of soldering NiCr and stainless steel connectors as well as hygroscopic core of the cable make the usage of Thermocoax less attractive.

The cable with 0.5mm outer diameter measured at room temperature showed 200dB/m attenuation at 20GHz as reported in [25]. At 4.2K similar cable showed  $\sim$ 100dB/m attenuation at 8GHz, while achieving  $\sim$ 20dB/m at 300MHz [24].

However, in order to get reasonable attenuation one has to use the length of the Thermocoax cable of at least 1m. In terms of the present task, this long cable has to be situated at the lowest temperature end of the cryostat for each of the 16 lines. This construction would be too bulky to fit the space limitations and meet the cooling thermal mass requirements.

#### Twisted pair filter.

This filter consists of a twisted pair of resistive wires wrapped tightly in copper tape. The copper tape acts both as a shield and as a ground to which the lines are capacitively coupled. The copper tape is pressed around the wires very closely so that the distance between the wires and the shield is that of the insulator thickness on the wires, about 10 microns. Thus there is a certain capacitance from the wires to ground as well as between the two wires in any given pair. This capacitance to ground combined with the high resistivity of the wires makes the cable a continuous RC line. In [26] 1.87m long copper filter with capacitance 210pF/m achieved less than -80dB attenuation at 20GHz being measured at room temperature [26].

This kind of filtering could be made with zero DC resistance if superconducting materials were used [27].

Again, the space limitations in current task make this design impossible to implement.

#### Metal powder filter

Another common method is to use metal powder filters. In general, the low-pass metal powder filter is an insulated wire surrounded by fine metal grains. The attenuation of a signal occurs due to the dissipation of high frequency current induced in the grains. The large surface area of a metal powder

results in significant skin-effect damping. Attenuation depends on several parameters, such as the powder material, the size of the grains, and the diameter and length of the wire. Stainless steel powder is often used. Also available on the market Eccosorb line of microwave absorbing materials. They are often chosen because of the possibility to get different magnetic-loading and dielectric embedding.

In ref. [24], the stainless steel powder filter in a cylindrical geometry with an SMA connector was discussed. The goal of this filter performance was more than 50dB attenuation at 1GHz measured at 4.2K. It was fabricated by drilling a 45mm long hole, 5.3 mm in diameter, through a copper block. 1.4 m of the copper wire was wound into a spiral around a tube with diameter 3.5 mm. Half of the spiral was counterwound to reduce the magnetic field pick up. One end of the copper wire was then soldered to the center pin of one connector. For proper performance of the filter, it was important that the coil had a constant pitch over its entire length in the powder and that it was not deformed. The center conductor was thereafter sealed with epoxy. After soldering and sealing the other connector, stainless steel powder was filled into the filter. The empty space over the powder was filled with epoxy and the remaining connector was pressed into place. Due to this fabrication process, these filters were inherently strongly asymmetric with respect to their reflection properties [28]. In the final filter most of the powder was loose inside, since the epoxy could not penetrate the densely packed powder. This might help to reduce stresses in the filter during cooldown. However, if the epoxy cracked, the fine grain metal powder would be spread over the sample stage area, making fatal contamination of the cryostat.

The stripline geometry simplifies the filter fabrication. It supports a TEM mode at low frequency, with higher order modes appearing when the enclosure begins to act as a waveguide. The study on stripe-like filters made of different Eccosorb materials is done in ref. [29]. Authors used the FGM-40, GDS, and MCS materials, which are magnetically-loaded silicone sheets, as well as the Eccosorb CR-124 material, which is a powder-loaded epoxy. There, the magnetic loading material is carbonyl iron or ferrite powder, or a combination of the two. Authors used rectangular enclosure, machined in a block of copper, had length 32mm, width 12-13mm, height 1.5-4.6mmm. It was filled with absorbing material. SMA receptacles with an extended dielectric and pin contact were mounted on each end of the copper block such that the pins extended into the center of the enclosure. The 0.15mm copper foil strip connected the pins. The examination presented in [29] showed that the epoxy-based CR-124 material has ~ -80dB attenuation at 4GHz measured at 4.2K. Analyzing thermal and filtering properties of the considered materials, the authors suggested that CR-124 is the most suitable material for sub-Kelvin measurements.

Bronze powder low-pass pi-section filters are used in low frequency current bias lines in qubit experiments [30]. They are essentially easy to heat sink. 0.105 in. diameter bronze powder/epoxy rod that is 6 in. long was made using a simple straw as a form and injecting it with a bronze powder/epoxy mixture. After hardening, Cu-clad 0.005 in. diameter NbTi wire was space-wound around the rod and glued with varnish. The total length of NbTi wire was roughly 20 ft. Then, 0.031 in. diameter cotton string wound spacer was glued in a coarse helix on top of the NbTi wire to center the rod when it is pushed inside the brass tube. The thickness of the string was chosen to give a tight fit. The brass tube was 0.218 in. o.d. x 0.015 in. wall x 6 in. long. These filters were made using SSMC "nanohex" connectors and  $0.01\mu$ F surface mount capacitors with an NPO dielectric, and therefore the capacitance did not change much with temperature. Two housings at the two ends of the filter partially filled with Stycast 2850 epoxy provided the thermal contact to the metal powder/epoxy rod and protected the electrical connections inside the housings. At 4.2K, the bronze pi-filter showed  $\sim$  -40dB attenuation at 3MHz.

#### Pi-filters with powder core

Taking into account the strong and weak points of the already developed cryogenic filters, the decision was made here to manufacture miniature LC Pi-filters with metal powder core. Main concept of the filter design is described very well in Ref. [31].

There are two main ways to surround a central wire with a metal powder: to use a pure powder or to mix it with epoxy. Since the metallic powder filter placed at low temperatures are used not only for the noise elimination, but also to thermalize the electric leads coming from the high temperature parts of a cryostat, the epoxy Stycast 2850FT mixture with the metal powder could be used. In this case the attenuation is a little less, but the thermalization of the central wire is much better.

One simple approach to make metal powder filters is the following. First, one usually prepares a coil using a thin insulated wire. To do this, one can take a rod, wind a wire around it, and after that remove the rod from the coil. Then it is necessary to place the coil into a metal box and fill its volume, both inside and outside the coil, with a mixture of metal powder and epoxy. Finally, it is essential to solder and mechanically fix the connectors and to close the jacket. As the epoxy may have relatively high viscosity, there is a risk of obtaining a nonhomogeneous spatial distribution of the powder due to the appearance of air bubbles. Together with a nonideal coil shape, this can result in additional unwanted resonances on the transmission characteristics of the filter. Moreover, due to the high viscosity of the epoxy it is difficult to fill the coil with a mixture with high enough powder content. Even if the powder-epoxy mixture is carefully degassed under vacuum, air bubbles are trapped during the process of pouring and casting.

Taking the above issues into account, a different approach was chosen.

#### 2.2.3 Filter fabrication

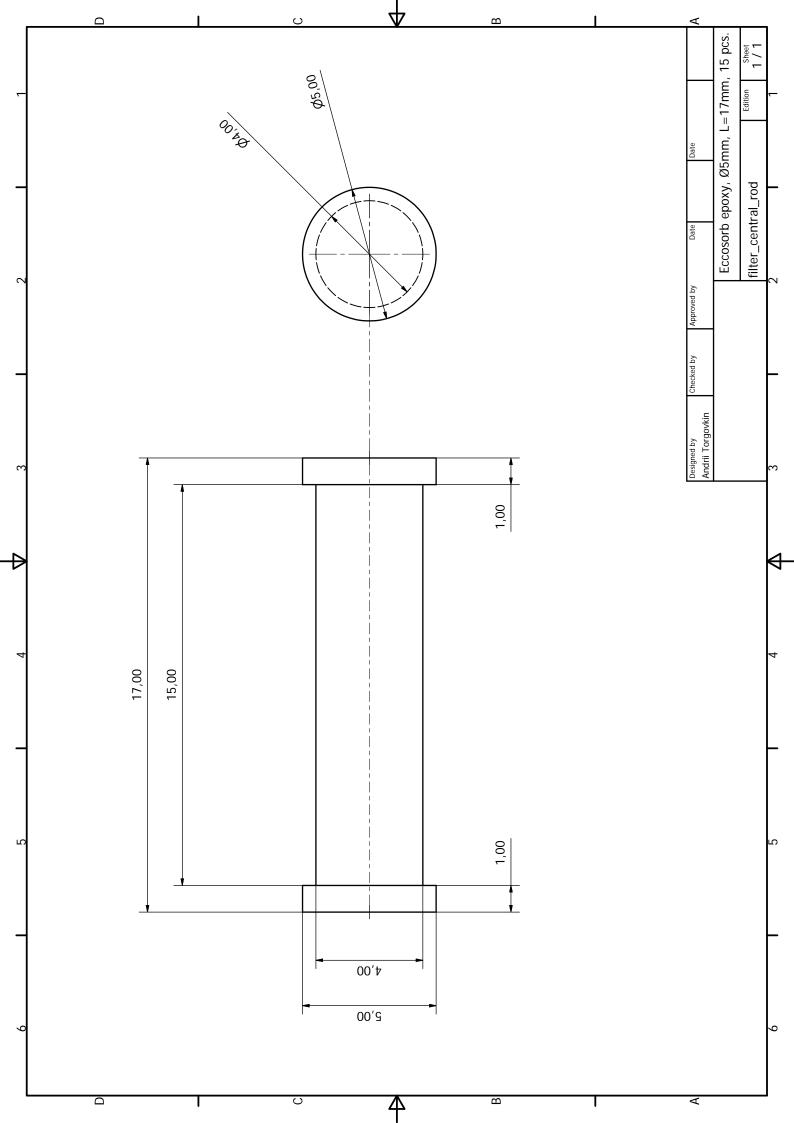

#### Eccosorb rod

First, a set of rods of powder-containing material was prepared. It was not evident that use of Stycast-2850FT in mixture with stainless steel powder would result in the best filtering properties. As a result, two sets of rods were prepared. One set was made out of the mixture of Stycast 2850-FT and metal powder and another set was based on the commercially available material Eccosorb CR-124, made by Emerson & Cuming.

Eccosorb CR-124 is an epoxy resin loaded with iron powder. It has very good absorption properties for electromagnetic radiation at high frequencies. Among other series, CR-124 is intended for use in lowest frequency range from 5GHz and higher. This series has also the highest mixing ratio for epoxy base and curing agent, which results in hardly pourable product, as the epoxy base has high viscosity itself. The recommended curing schedule requires heating of the epoxy to 75°C during 12 hours. The experimental analysis in Ref. [32] shows for this epoxy that "the cooling capacity required to cool Eccosorb CR-124 from 4.2 (1.6) K to 50 mK is approximately 6.2 (5.4) times smaller than the cooling capacity required to cool an equal mass of copper from 4.2 (1.6) K to 50 mK". The authors also estimate that the mass fraction of the iron filler in Eccosorb CR-124 could be as high as 60%.

Eccosorb epoxy base was warmed up to 70°C using water heat bath on thermostabilized magnetic stirring device. A PVC cup containing 20g of epoxy base was immersed into 30ml of hot water in wide and low-height chemical glass. The heating process was done inside a fume hood to prevent excess water vapor condensation on the epoxy, and was controlled manually with the help of remote electronic thermometer. The epoxy base slightly lowered its viscosity in the hot state. Next, 0.4g of hardener was added to the cup and manually mixed with the help of clean plastic rod. Mixing was done for 2 minutes after which the mixture was taken out of the hot water bath and put under vacuum conditions (5-7 torr) to eliminate trapped air bubbles. The vacuum treatment lasted for 120seconds, during which the material cooled down and substantially increased its viscosity, making further bubble flow difficult. After degassing, the epoxy was heated and poured into a preheated mold of cylindrical shape. The epoxy was cured at 75°C for 12 hours.

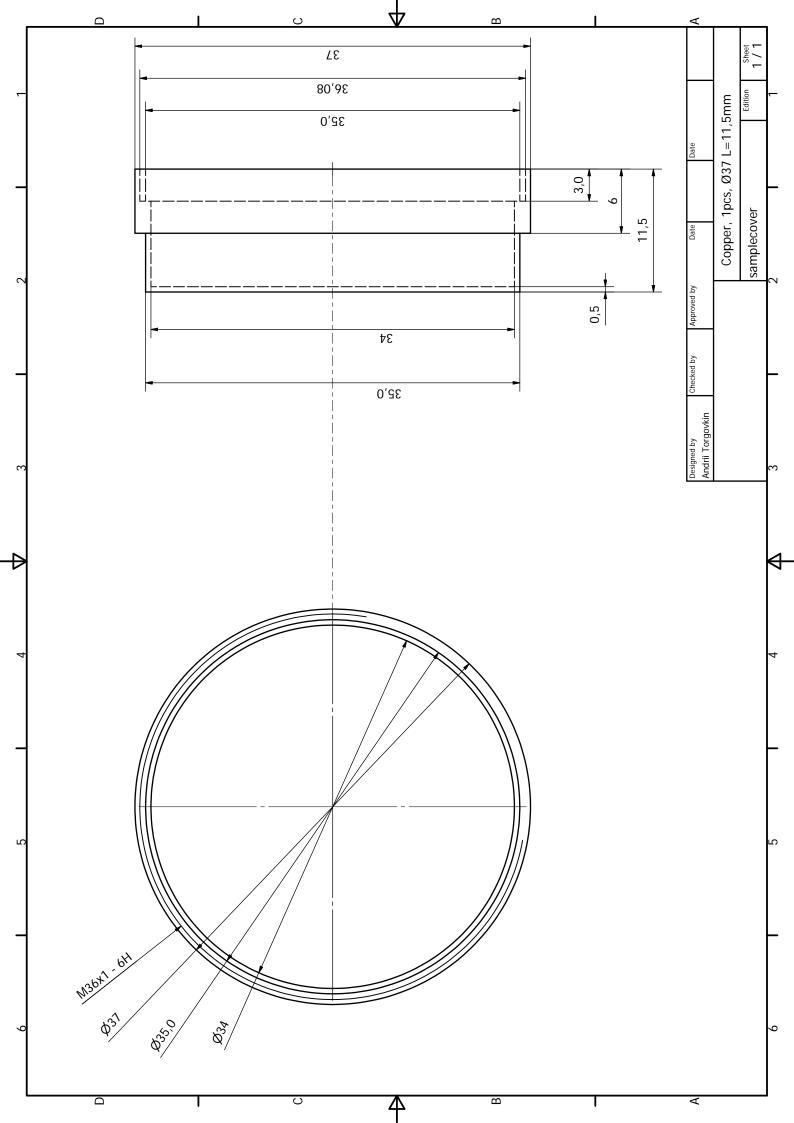

#### Pi-filter

During the second step, the internal parts of the filters were made.

After curing, the resulted rod was machined into small bobbins, 4mm in diameter and 15mm long with 5mm diameter flanges. One layer of copper wire was used to make a coil (see Fig. 2.4) The coil consisted of 114 turns of 0.05mm insulated copper wire, with no separation between turns. Direct calculation gives a number of 300 turns to be made, but one must take into account the thickness of insulation and the necessity to leave a gap between the coil and the flange of the bobbin. The wire escaped the bobbin through a 0.5mm notch purposely made in each flange and was glued to the ends of the bobbin with GE IMI 7031 varnish.

Pi-filters require capacitors to be installed on both sides of the coil (see Fig. 2.3 b). Regular SMD components could not be used, as the targeted frequencies to be filtered are in the range of 10 GHz and higher. At such a high frequencies significant power can pass through the circuit element and hit the sample. As filters were designed to have axial symmetry, the decision was made to use discoidal capacitors, as they could improve noise confinement inside the filtering volume. Also components of this type are made of ceramics and have low thermal expansion coefficients, and are thus suitable for applications at cryogenic temperatures. Miniature discoidal feed-through capacitors were purchased from Pacific Aerospace & Electronics (PA&E) company, part number FC200N472M500-050-050-C. The capacitance value is 4.7nF. These capacitors with dimensions of 5mm in diameter and 1mm in height could be glued with varnish to the coil ends.

The copper wire wound onto the spool was pre-tinned and soldered to the inner electrode of the capacitor on one side of the filter core. At the other side, a miniature MCX connector was soldered to the capacitor first. Prior to soldering the connector, all the pins were cut down to make the soldering side flat and round, except for the central pin, which was left 1mm long. Finally, the central pin was soldered to the capacitor center electrode and the shell was soldered to the outer, ground electrode. The signal is carried through the central electrode of the capacitor to the central pin of the connector.

**Figure 2.4.** Filter core with copper coil, two capacitors and one MCX connector. The schematic picture of the discoidal capacitor is also shown (capacitor image is taken from the PA&E official catalog).

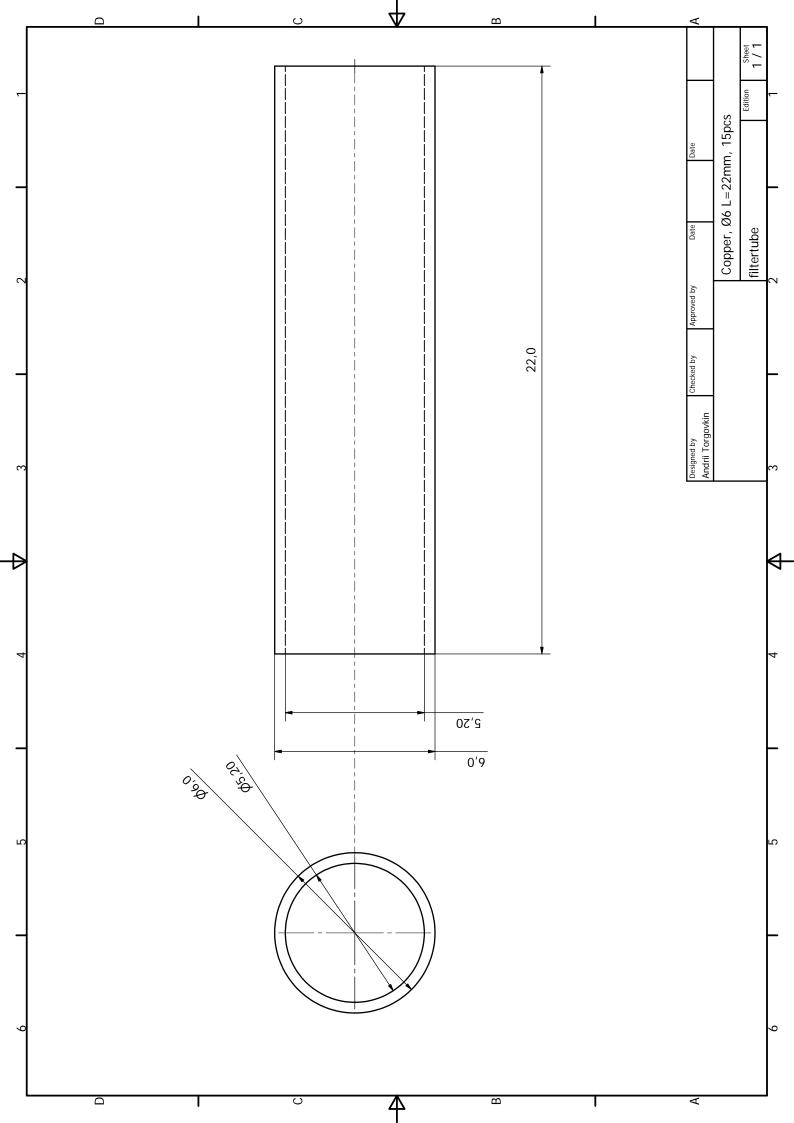

#### **Packaging**

Finally, the filter was packaged into a copper shield, consisting of a 26mm long tube with outer diameter of 6mm and inner diameter of 5.5mm. Copper was chosen, as it is a material with high electrical and thermal conductivities, is non-magnetic and non-superconductive, as magnetic fields trapped inside superconductor could significantly influence experimental results. The softness of copper makes it very difficult to machine cut the tube with such thin 0.25mm walls, and special attention has to be paid to the inner surface quality and roundness of the tube.

The filter core was inserted into the copper tube so that the end with the capacitor without the connector was immersed into the tube by half of the capacitor's height. The filter core end with the MCX connector was carefully filed free of solder leftovers, in order to fit the 5.5mm diameter hole tightly. However, an air gap of 0.65mm would be left between the copper tube and the wire winding, which could serve as a waveguide for high-frequency radiation. One straightforward way to block this radiation is to supply Eccosorb into the gap. But extreme viscosity of the hardened Eccosorb leads to formation of air pockets and uneven filling of the tubular airgap. Thus, the decision was made not to use Eccosorb but use epoxy loaded with stainless steel powder (SSP) instead. Stycast 2850FT with Catalyst 24LV was loaded by fine 50 micron stainless steel powder 50% by weight. After mixing the epoxy primer with

catalyst and powder, it was kept under vacuum in order to remove air bubbles trapped into the viscous mixture during mixing.

Degassing of the epoxy mixture should be done in pulsed way. When a highly viscous mixture is first exposed to vacuum conditions with pressure lower than 100mbar it may raise a foam rapidly and evenly in the mixture volume, and contaminate the vacuum chamber with epoxy. Pressure should be lowered in a slow, controlled manner to keep the foam inside the cup container. After the first foam formation, one should leave the chamber at constant pressure for a short while, so that larger air bubbles have time to float to the mixture's surface. If one fills the vacuum chamber with atmospheric pressure at this point, the foam inside the mixture volume will fall but the floated bubbles will decrease in size and rest on the sidewalls of the cup, inside a thin layer of mixture. During the next vacuum exposure, these sidewall bubbles are more likely to burst efficiently before the main volume foam rises for next time. Epoxy degassing should not be done continuously for a long time, as it increases its viscosity over time both by hardening, which is normal process, and by evaporation of the hardener, which may lead to poor quality product.

Powder-epoxy mixture was finally applied into the air gap by a narrow syringe with a short needle. The filter core was moved inside the copper tube simultaneously while applying the epoxy mixture. The epoxy was left to dry for 24 hours at room temperature. Filter was left in a vertical position with the MCX connector pointing down, as the solder leftovers at this end were serving as stopper, preventing epoxy release.

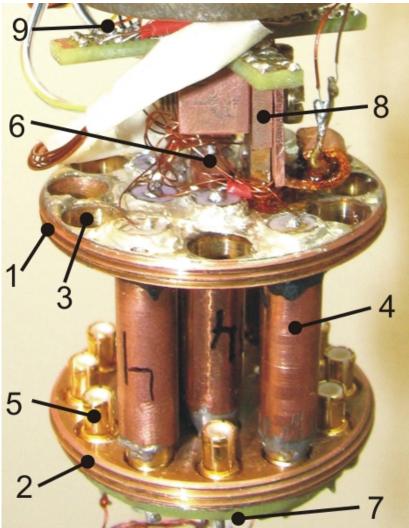

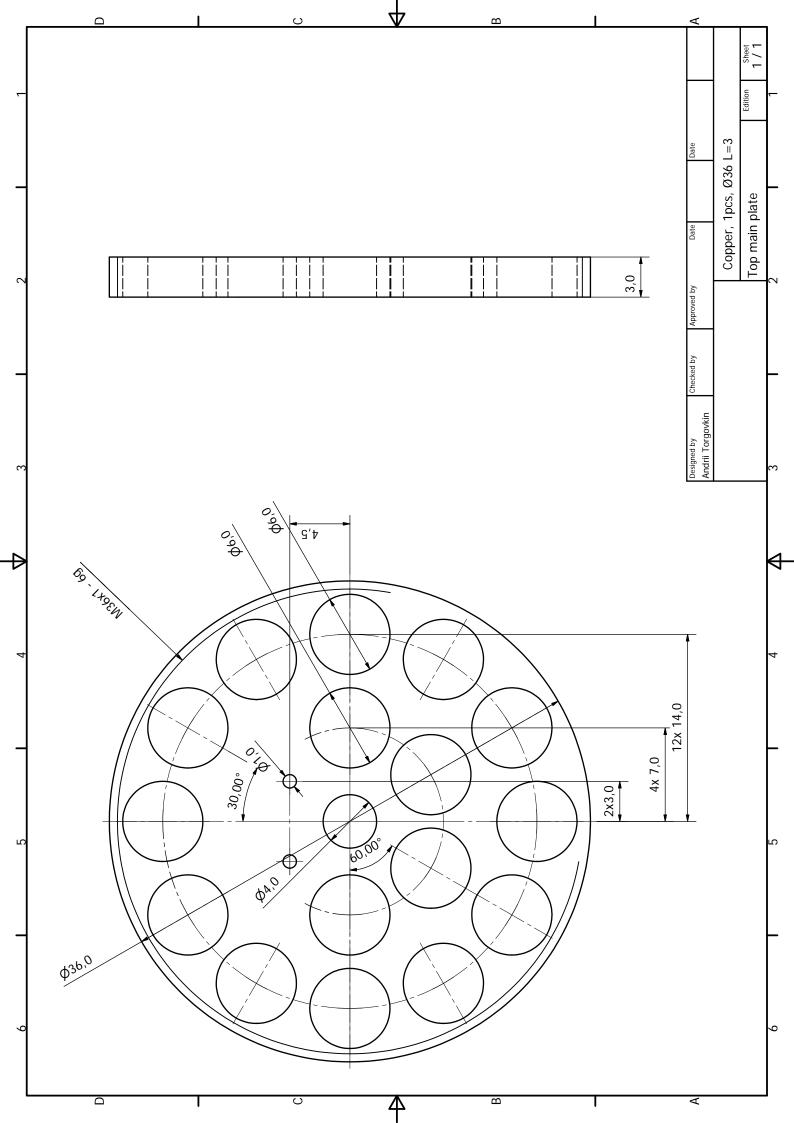

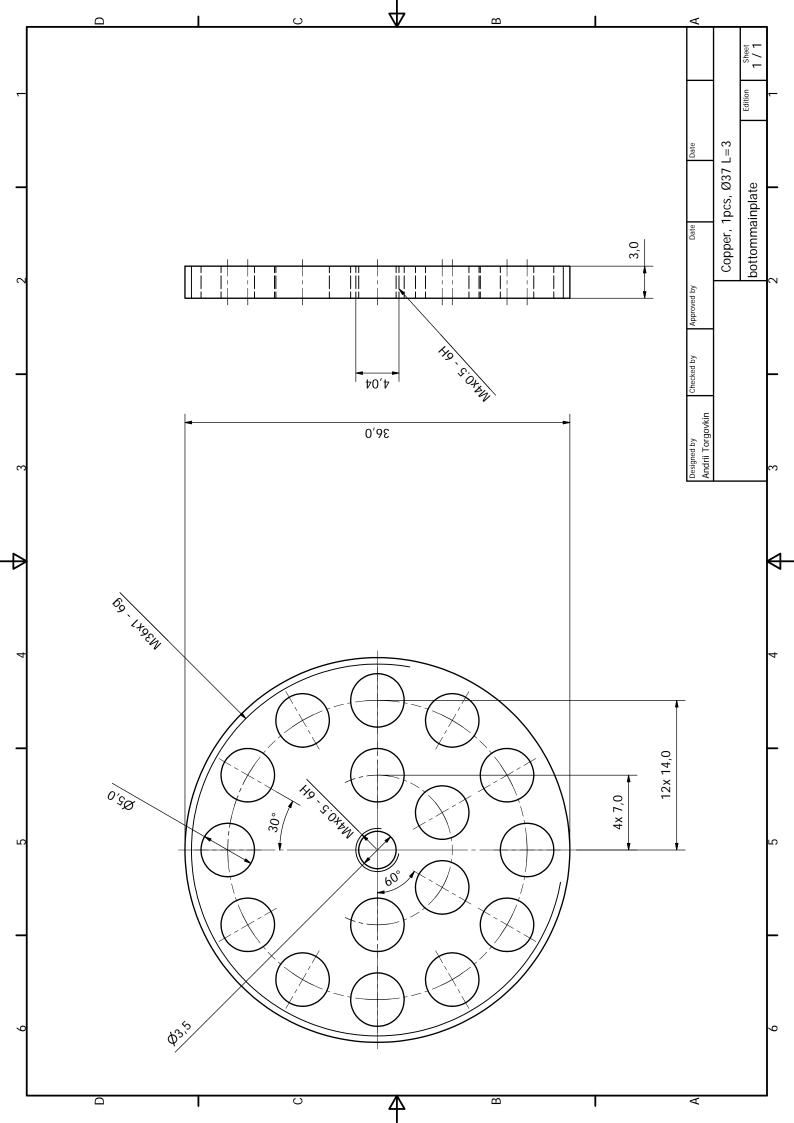

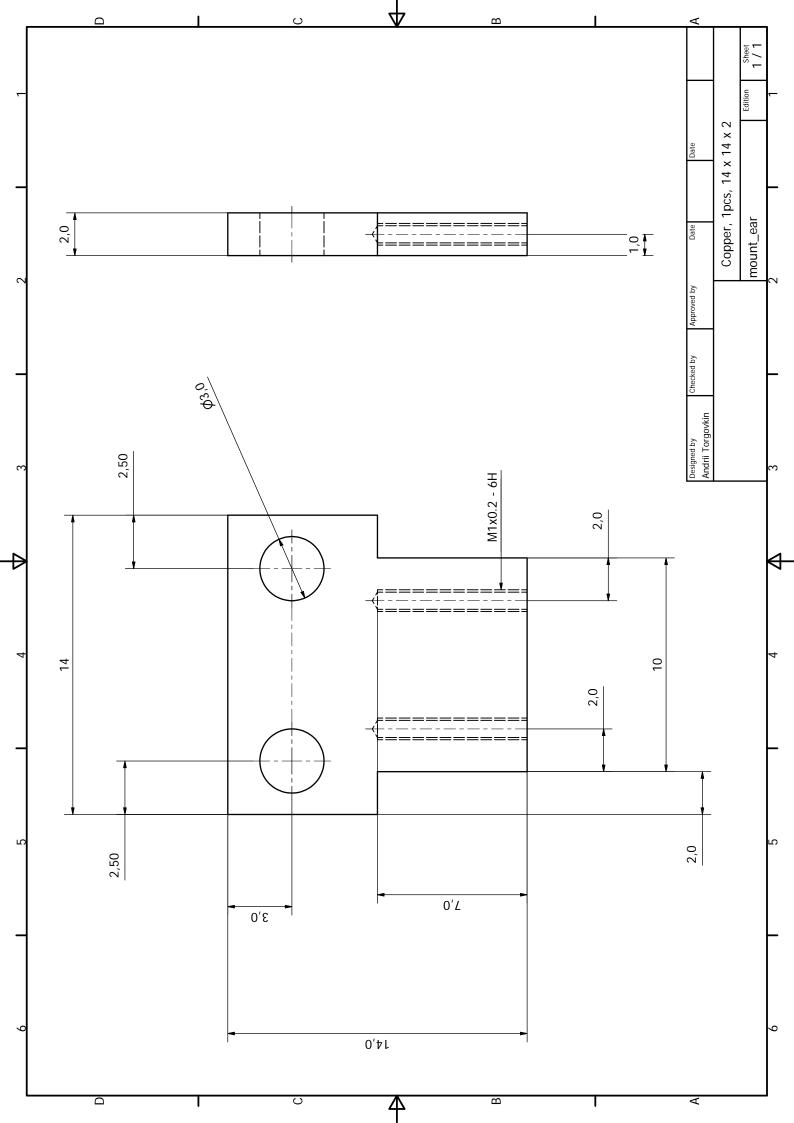

#### 2.3 Sample stage.

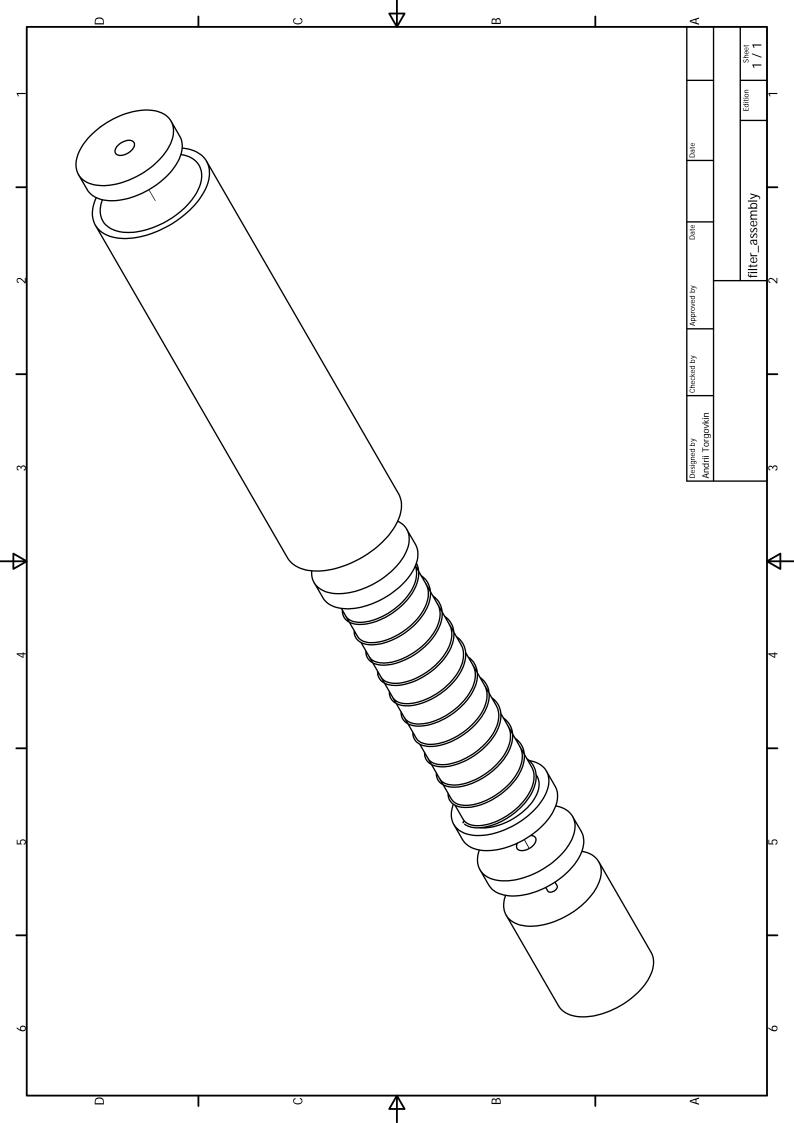

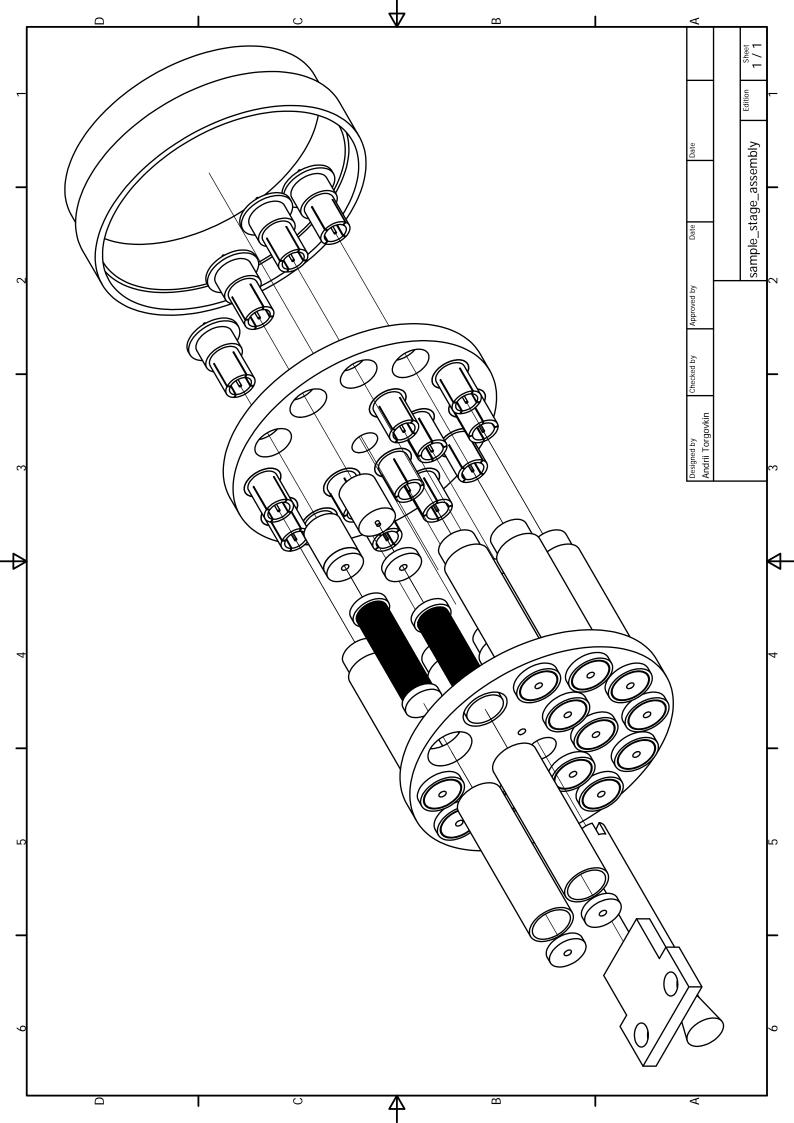

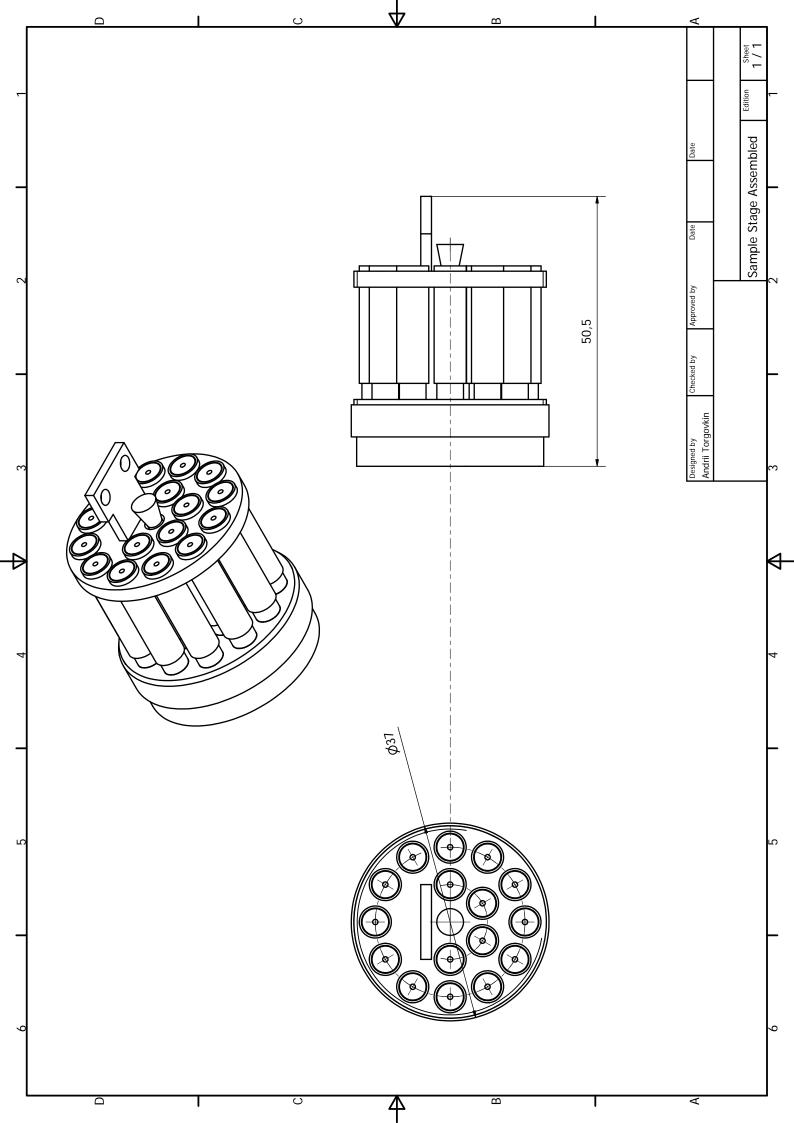

In order to incorporate new microwave high-frequency (HF) radiation filters into an existing dilution refrigerator, a new sample stage was designed. The machine drawings of the sample stage are shown in Appendix A.

The design objectives that had to be reached for the sample stage included placing of 16 HF filters into a limited space. The vacuum jacket of the cryostat restricts the size of the sample stage to a cylinder with diameter 40mm and height 55mm with sample cover attached. This space has to accommodate not only the filters but also the necessary supporting structures and mounting hardware, as well as provide sufficiently easy access for repairing.

In the sample stage design most elements have cylindrical symmetry with their axes aligned along the cryostat main axis. A photograph of the assembled sample stage half-filled with filters is presented in Fig 2.5.

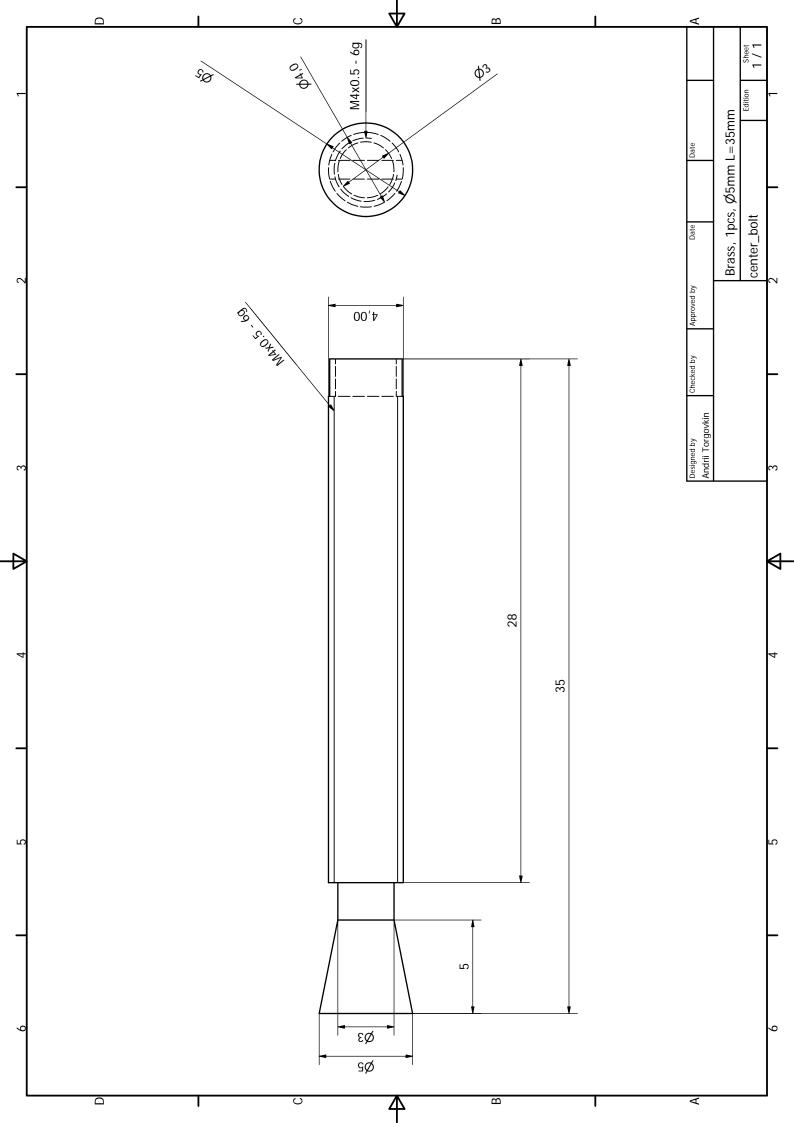

The sample stage consists of two plates with holes to accommodate filters. Both upper (marked in Fig 2.5 as 1) and lower (2) plates have sixteen holes (3) for filters (4) and connectors (5) and one central 4mm hole for central rod (6). The bottom plate has M4 thread in the central hole, so that the threaded central rod can be twisted in there. The bottom plate is filled with complementary ("male"-type) MCX connectors (5) that have their center pins soldered to the PCB (7) containing thermally anchored place and electric contact pads for the samples.

Due to the fact that even single MCX connector is engaged very tightly, handling of 16 of them must be done very carefully. Central rod serves to this purpose. It is restricted from movement along its axis in the upper plate, and when it is screwed in to the bottom plate MCX connectors are engaged. The central rod also serves as an additional thermal link between upper and lower plates.

Holes for the filters are placed symmetrically in order not to unbalance the sample stage. Upper plate is equipped with a perpendicular support element (8), which is tightly fitted to the mounting silver screw, which is attached to the mixing chamber sintered plate of the cryostat. As the mixing chamber is constructed from plastic inside heat exchanger, there is a plastic-to-metal interface at the point where the silver mounting screw enters the plastic part. Any off-axis load applied to this interface may create a leak

that can lead to <sup>3</sup>He-<sup>4</sup>He mixture loss from the mixing chamber. Also any uncompensated strain of the plastic heat exchanger can induce its permanent bending and make the sample stage to touch the walls of the vacuum jacket.

All supporting structural elements were made of copper to ensure good thermal conductivity. Filters were tightly fitted to the holes of the top copper plate and glued with the Stycast 2850FT from one side, and with silver-containing conductive epoxy at the discoidal capacitors end. Both copper plates have an outside thread, designed for sample cover cap that can be attached. Covering the sample area below lower copper plate makes the volume shielded from thermal radiation and unnecessary electric signals. Thus, the only way for the measurement signals to enter the sample stage is through the metal powder filters. Measurement lines as well as technological lines that are wrapped around the plastic heat exchanger are soldered to an intermediate cross-like PCB (9) for ease of repair, as high resistance manganin wires are very brittle and should not be bent many times. Starting from the PCB down to the filters, copper wires are used. There is no reason to restrict heat conduction by wires at this segment, as the cross-like PCB is already anchored to the lowest temperature end of the cryostat.

**Figure 2.5.** The scheme of the sample stage. 1 – upper plate; 2 – lower plate; 3 – hole 6mm in diameter; 4 – metal powder filter in a shield; 5 – MCX connector; 6 – central rod; 7 – PCB with contact pads; 8 – support element; 9 – intermediate cross-like PCB.

## 2.4 Evaluation of high frequency filters.

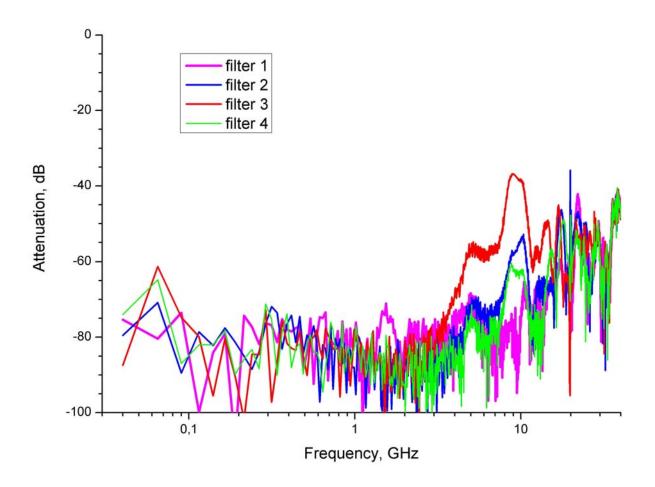

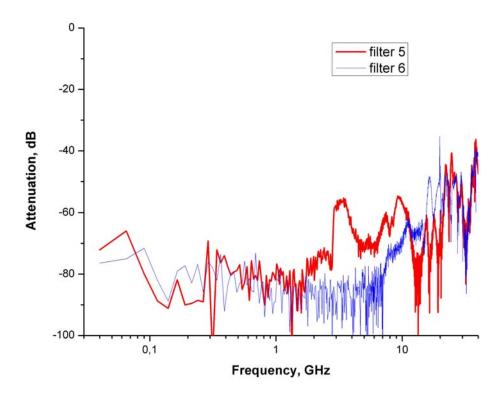

All filters were measured independently for their frequency response using a vector network analyzer ANRITSU 37369D, which is capable of measurements from 40MHz up to 40GHz. In terms of S-parameters, S<sub>21</sub> characteristics of each filter were measured.

Measurements were done at room temperature and at 77K, however the lower temperature results were not qualitatively different from the room temperature ones. The resulting frequency response curves are shown in Figs 2.6 – Fig 2.11. During the measurement the input power level was set to -6dBm (0.25mW). Due to the fact that each filter does not have connector at one end by design, the MCX connector was soldered to that end purposely for measurements and desoldered before installation to the sample stage. Measurement lines of the network analyzer were equipped with SMA connectors by default, and SMA-to-MCX interface connectors were used.

Figure 2.6. The frequency response of the filters marked 1, 2, 3 and 4.

**Figure 2.7.** The frequency response of the filters marked 5 and 6.

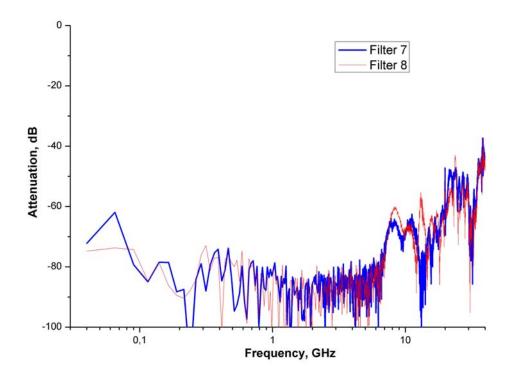

**Figure 2.8.** The frequency response of the filters marked 7 and 8.

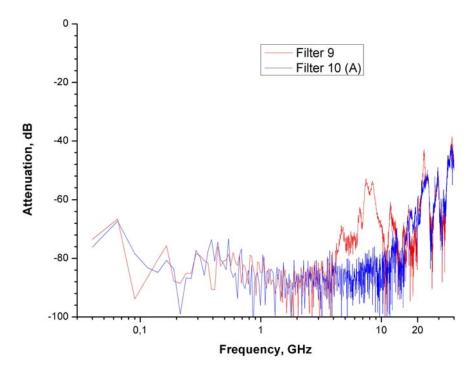

Figure 2.9. The frequency response of the filters marked 9 and 10.

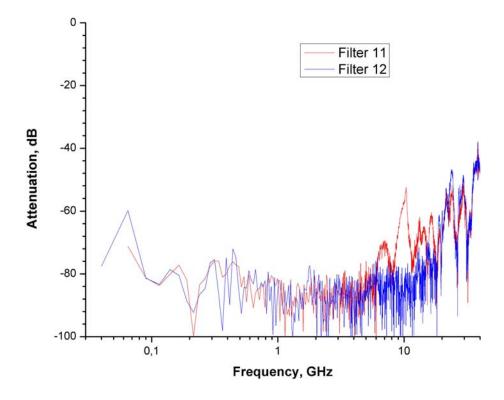

**Figure 2.10.** The frequency response of the filters marked 11 and 12.

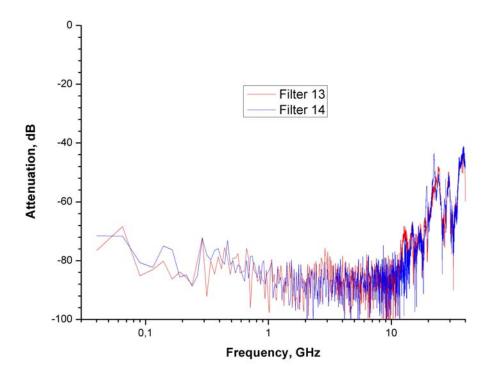

**Figure 2.11.** The frequency response of the filters marked 13 and 14.

The filters marked 1, 2, 3, 4, 5 and 6 were fabricated with the coil core made out of metal powder – epoxy mixture. The rest of filters used Eccosorb CR 124 as the core material. The measured characteristics did not show systematic differences in high-frequency behavior between these two sets.

After the filters were installed to the cryostat, high-frequency measurements became impossible, as the measurement lines in the cryostat were not shielded. The excitation RF signal from the network analyzer in the input line would be picked up by the return line without being passed through and attenuated by the filters at the sample stage.

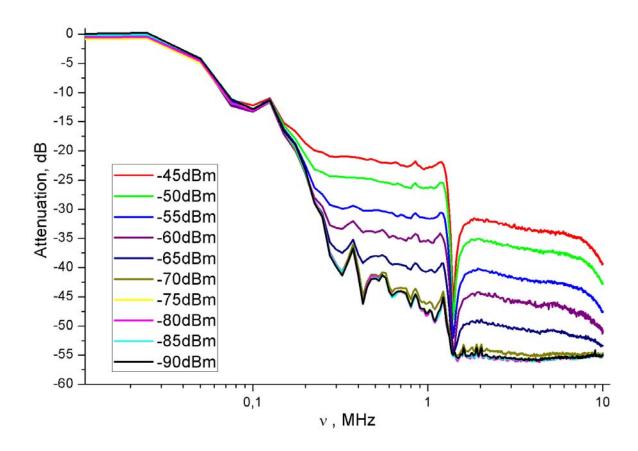

The overall cryostat filtering frequency response at low frequencies up to 10MHz is shown in Fig 2.12. The measurement was done with the sample stage temperature of 100mK through two measurement lines, containing the low temperature Pi-filter, a microstrip filter at 1K and one LC filter at 4.2K each. The frequency spectrum was measured with an Agilent 89410A network analyzer, capable of measurements from DC to 10MHz. The excitation signal was preset to several different values during this measurement, in order to get a full picture of the transmission characteristics.

**Figure 2.12.** Frequency response of the cryostat measured at different excitation power values.

#### 2.5 Discussion about filter characteristics

As it can be seen from the Fig 2.6 – Fig 2.11, each filter has an attenuation  $\sim 80 dB$  in the frequency range 40 MHz - 2 GHz. This fact allows proper filtering out of the thermal noise from the sample stage.

In the band 2GHz- 10GHz several filters showed non-systematically appearing broad resonance peaks. These peaks might appear due to non-homogeneous distribution of the SSP-epoxy mixture inside the gap between the filter core and the copper shield. Another possible reason for seeing resonance peaks is a low quality joint of the MCX connector that had to be soldered to one of the filter's ends to conduct measurements with the network analyzer. This MCX connector was not soldered permanently, possibly leaving an air gap between the grounding shell of the connector and the copper shield of the filter. An air gap could provide another pathway for the excitation signal of the network analyzer. In that case, the measured data does not represent actual attenuation of the filter in the frequency region of the resonance meaning that the real attenuation could be higher

At frequencies higher than 10GHz the noise floor of the measurement setup increased gradually with the increase in frequency. This might have happened because of poor soldering of the second MCX connector to the filter.

The data presented in Fig 2.12 were measured in order to test the actual filtering cut-off frequency of the cryostat in the frequency range below 10 MHz. This figure clearly shows the fact that during the measurement of the frequency response of the cryostat the excitation signal from the network analyzer was picked up by the return line without passing through filtering at high enough frequencies. In

the frequency region starting from 150kHz, one can clearly see that attenuation curves are equidistantly separated in magnitude, and this separation matches the 5dBm steps for input power until the input power drops to -70dBm (0.1nW). At power levels lower than 0.1nW the curves coincide.

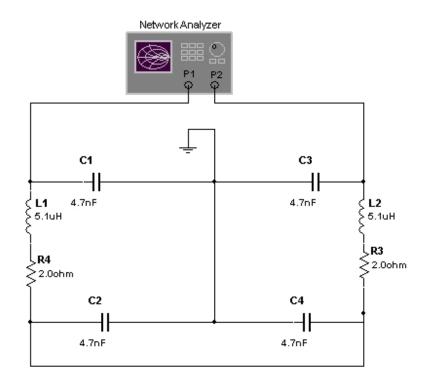

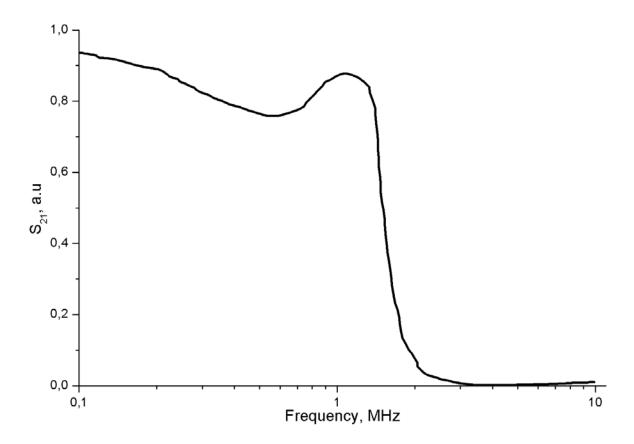

There is also a resonance feature located at the frequency of 1.4MHz. This is in a good agreement with the simulation results of the simple circuit model presented in Fig 2.13. In the simulation, only two Pi-filters are included in order to get the frequency response of the sample stage without the subsequent filtering located at the 4.2K stage. The inductance value is taken as  $5.1~\mu\text{H}$ , which was measured on a sample of a coil of copper wire on Eccosorb core with the same dimensions as in the actual filters.

The result of the circuit simulation is presented in Fig 2.14. One can see that the simulated curve has strong cut-off at 1.4MHz, following after a small resonance peak. Similar behavior is seen in Fig 2.12 on every curve which is above -70 dBm of input power. The strong attenuation peak at 1.4MHz originates from the parallel resonance nature of the double Pi-filter circuit.

**Figure 2.13.** The equivalent circuit used for simulations of sample stage frequency response.

**Figure 2.14.** The simulated sample stage frequency response shows the position of the cut-off frequency at 1.4MHz.

As a result, one can conclude that measurement setup enables measurements up to moderate frequencies of  $\sim 25 \mathrm{kHz}$  without significant attenuation by the filtering.

#### 3. SINIS thermometer sample

#### 3.1 Sample overview

There is a need of a good temperature sensing device in the region below 1K. One simple choice is to use SINIS junctions made of aluminium and copper. The insulating layer is then the native aluminium oxide. A sample of this type can be fabricated in a very controllable way.

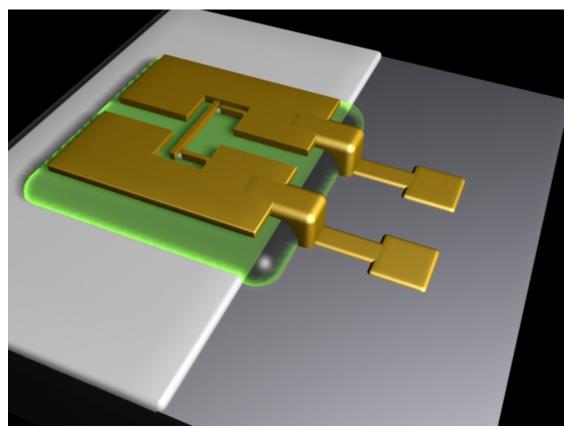

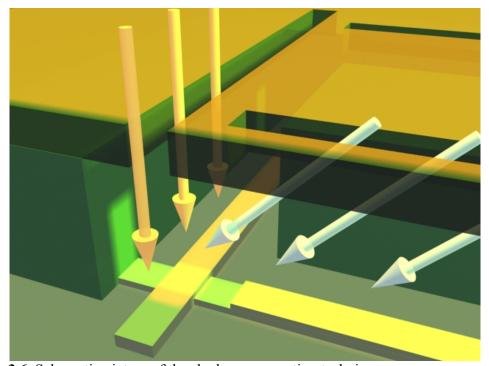

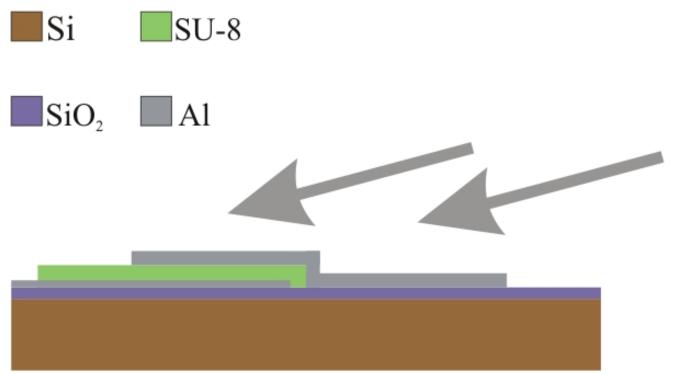

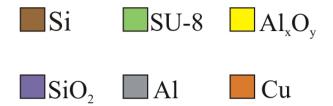

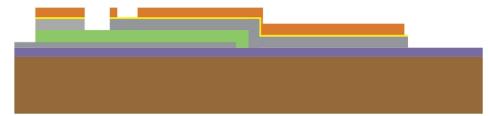

In this thesis, we want to investigate, if an on-chip capacitor can be fabricated together with the SINIS junction, to create another filtering stage on-chip. In order to make the capacitance on the chip, one should introduce two large area electrodes to the sample. Thus the technology of this SINIS-sample fabrication is slightly different from the reference sources [6, 14, 18, 19]. The idealized 3D model of a desired sample is shown in Fig 3.1.

Figure 3.5. Idealized sample 3D modeling (schematics).

It was decided that two samples should be made. The first sample should have one electrode as a ground plane underneath, an insulation layer of reasonable material with reasonable thickness, and the second electrode as a part of sample structure on top. The second sample would be the same, but without on-chip capacitor. The substrate was chosen to be a positively doped Si wafer with a 300nm layer of thermally grown native oxide.

# 3.2 Sample fabrication steps.

Due to certain restrictions in fabrication facilities, in particular, the small writing field of the electron-beam lithography machine, the maximum size of the sample was chosen to be 2 by 2 mm. This area had to be divided equally to make the two electrodes of the capacitors. In order to maximize the capacitance, only one SINIS junction was designed to fit one sample. So, each of the top electrodes can be fabricated on the area of approximately 2 by 1 millimeters.

The SINIS junction was designed to fit the center area of the capacitor to simplify the writing field alignment during the electron beam lithography. A schematic of the sample design is shown in Fig. 3.2 and Fig. 3.5.

The fabrication procedure included the following steps:

#### 3.2.1 Substrate cutting.

The silicon substrate was p-doped with boron, having the holes as majority charge carriers. This choice was done in order to minimize the electrical conductance of the substrate at low temperatures, as the mobility of holes is lower than that for electrons at low temperatures.

Original 150mm diameter wafer was cut to stripes of 32mm width to fit the oxidizing oven.

#### 3.2.2 Substrate cleaning.

This step is very essential for further processing and sample performance. If any dust particles were left on the Si surface, they might prevent the formation a uniform layer of dielectric silicon oxide, and lead to the formation of so-called "pinholes" in it.

A pinhole is recognized as an area on the substrate, in which the sample structure will have an electrical connection to the substrate common ground. Thus, if several different wires of the sample will be shunted to the common ground, this may destroy any measurement results. Unfortunately, pinholes cannot always be totally avoided, but their number and their effect can be significantly reduced.

Clean original Si chips should not have any contamination, of which major are: silicon dust from the cutting process, organic leftovers and fingerprints, airborne dust particles. All the dust particles with a weak bonding to the surface can be blown out of it using pressurized air, but other ones require wet cleaning to remove.

First, Si chips were dipped into boiling acetone for 2 minutes to remove any soluble organic contamination. Next, chips were dipped to isopropyl alcohol (2-propanol, IPA) and placed in the ultrasonic bath for 20 minutes, and this was repeated 3 times with changing of the cleaning liquid before each time. The ultrasonic device used was made by FinnSonic and is a temperature stabilized water bath to which ultrasonic power is coupled. While being in the ultrasonic bath, Si chips were oriented with the polished surface facing to the bottom of the glass. This ensures that the gravitational pull will not bring any particles to the working polished surface.

After the cleaning procedure, Si chips still stay under the liquid until equipment for the next step is prepared. Polished surface has to be exposed to air for the shortest possible time to prevent airborne particle accumulation.

#### 3.2.3 Substrate oxidizing.

After cleaning, the silicon chips were oxidized in order to form a primary insulating layer of SiO<sub>2</sub>. Thermal oxidation process was chosen as the most reliable and controllable. During this process, Si chips are heated to 1100°C in a nitrogen atmosphere and then exposed to oxygen for a certain period of time. This time determines the thickness of the resulting silicon dioxide. The temperature of the oven also influences the thickness and quality of the oxide, thus it was set to maximum possible on the available oven. A 350nm thick SiOx film was obtained with the process of 8 hours of oxidizing and a slow cooldown period of 7 hours.

#### 3.2.4 Sample chip preparation

After oxidizing the 32mm wide silicon chip was cut to smaller dice that fit the sample stage mounting plate. In particular, 8mm by 8mm size was chosen. At this point each chip had to be cleaned one more time to remove silicon dust left after dicing and to ensure that surface is flat.

Cleaning procedure for the small chips is similar to that of the bigger ones. Wet cleaning in hot acetone and ultrasonic bath of 2-propanol is the starting point. Chips also had to be dried of 2-propanol with a jet of dry nitrogen gas. However, optical microscope observations in the dark-field mode revealed that wet cleaning step is not sufficient, and the surface quality is still bad. As one can see in Fig. 3.2, there were aggregates and droplets left on the chip. Wet cleaning itself may be a possible source of these slowly evaporating droplets. Because contaminants were introduced by organic solvents, one can assume

that they are organic compounds themselves. This fact gives us a chance to remove them by selective etching with a highly reactive gas. Thus, dry cleaning with oxygen plasma was chosen as an appropriate

next step.

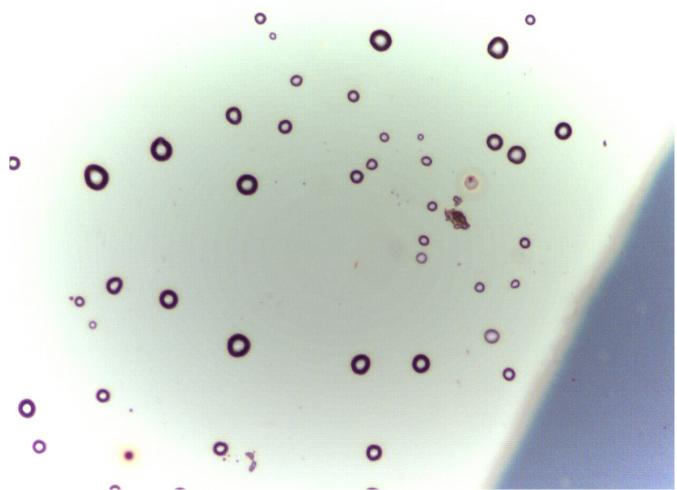

Figure 3.2. The surface of the Si chip after wet cleaning. Dark field optical micrograph, 20X.

Plasma cleaning with oxygen provides excited oxygen molecules and ions, which can hit the surface of the sample. In this particular case, the silicon has already been covered by SiOx, so that the interaction with oxygen plasma was not going to change the existing surface properties.

Cleaning was done with the help of Oxford Instruments Plasmalab 80 system, which is fully automated and computer controlled. Samples were loaded to the main chamber, which was evacuated to reach the pressure of  $2.5*10^{-5}$  Torr, filled with oxygen at 400mTorr and subjected to 200W of RF power. Substrate was exposed to high-frequency plasma for 20 minutes. After plasma cleaning, the substrate chip was immediately put to a clean container and moved to the next processing step.

#### 3.2.5 Back gate formation

In this step the first electrode of the designed capacitor was formed. This electrode will be connected to the common electrical ground during the measurement, so it must not be entirely covered by the structure later on. Due to the fact that wet etching in a base will be used for further cleaning purposes (see below) it was decided to deposit two metal layers on the chip. The first layer to be deposited was 45nm of silver, and the second layer was 60nm of aluminium. The silver layer is less

sensitive to wet etching with a base solution, and it remains at the areas where aluminium would be etched. The sample design requires that the back gate has to be formed only on one half of the substrate chip. Another one half of the chip area remains intact (see Fig. 3.1).

Metal deposition took place in the Ultra High Vacuum metal evaporator (UHV) which operates on the principle of electron beam evaporation. The electron gun generates a current of accelerated electrons that hits a metal target, releasing heat and thus causes the target to melt and evaporate its material. The conditions of the inner chamber were kept in vacuum below 10<sup>-8</sup> mbar, enabling ballistic transport of the evaporated material molecules. Ballistic transport of the molecules allows the so called shadow evaporation, when a 3D structure placed over the chip is making a shadow for the evaporated material. By controlling the shading patterns and choosing the proper angles of deposition, one can make complex structures on chip.

The evaporated material was deposited on the inner walls of the vacuum chamber as well as on the sample. The evaporator provided a possibility to change the incident angle of the material that was deposited to the sample by rotating the sample holder around one axis.

One half of the sample area was shadowed by the holding clamp of the evaporator sample stage during the evaporation. Evaporation of metals took place at an angle of 10 degrees to the surface normal, and aluminium was evaporated on top of silver without exposing the silver layer to air. The evaporation speed for silver was chosen to be  $0.5 \, \text{nm/s}$  and evaporation speed for aluminium  $-0.1 \, \text{nm/s}$ . The sample was finally exposed to 500 mbars of pure oxygen for 1 minute before exposing to air, in order to ensure the formation of an aluminium oxide layer. Angular evaporation was carried out in order to form shadows from possible contaminating particles and to break the layer of silver at pinholes.

#### 3.2.6 Insulating layer formation

On-chip planar capacitor requires an insulating layer to be formed. Taking into account that part of the back gate should not be covered with anything to facilitate bonding, full coverage of the chip with an insulator is not appropriate.

One way to make a suitable dielectric layer is to introduce a shadow mask to the chip and deposit e.g. silicon nitride with the use of PECVD technology. This was tried, but lead to the formation of very large number of micro-cracks in the silicon nitride layer, which in turn provided leakage path to ground. Thus, brittle materials should be avoided, and the choice of negative photoresist epoxy as an insulator seemed promising.

The negative photoresist epoxy SU-8 (from Microchem) was chosen as soft and non-cracking dielectric. In order to get a reasonable thickness of the layer, the initial solution was thinned 1/10 first and then 1/4 with cyclopentanone. The required final insulator thickness was about 800nm, but this was deposited in four steps of 200nm each. The thickness of each layer was determined with the help of an atomic force microscope on a calibration sample, which was made with the same deposition parameters as an actual sample. The advantage of the photoresist multiple layer formation is utilized, as it will be shown below.

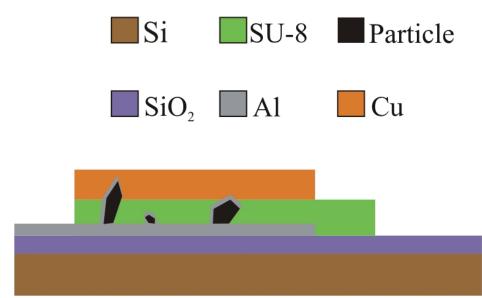

The sample chip was spin-coated with one layer of SU-8 at 5000 rpm for 45 seconds and dried at 95C for 3 minutes. After that, electron beam lithography was carried out with the Raith LEO 1430 scanning electron microscope. The pattern transferred to the resist was a simple square of 3mm size, and the exposure parameters were following: specimen current of -17nA, writefield 4096 micrometers, resist sensitivity 260, area step size 1 micrometer, dose factor 250%. The position of 3mm by 3mm square was chosen to be on top of back gate, but still letting 0.5mm to be over the region where there was no metal deposited (see Fig. 3.3 and Fig. 3.4).

**Figure 3.3.** Sample schematics. Pinholes and particles in the insulating SU-8 layer are shown in black. In this configuration there is a short from top electrode to the bottom.

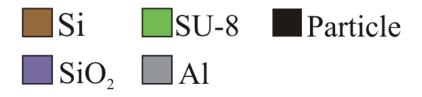

**Figure 3.4.** Sample schematics. After the NaOH etch and covering of the etched pinholes by another layer of SU-8 there will be no shorts formed.

After the electron beam exposure, the chip was heat treated for 1 minute at 95°C. Developing of the SU-8 was done with the use of acetone, as it will remove the unexposed regions of the resist. Exposed SU-8 resist will remain in place.

After development the sample was put to an etching medium for 120 seconds, which is 1M solution of NaOH in deionized water. This step is essential for further performance of the sample, as it helps to minimize the influence of the pinholes in the insulating layer of the capacitor. Because of deposited aluminium, each source of the pinhole was covered by this metal (see Fig 3.3, Fig 3.4). If the

particle is smaller than the thickness of the first layer of SU-8, it may not cause problems to insulation because it will be covered by the resist, and will not shunt the sample to the ground plate. But if the particle is higher, it will provide an electrical contact to the back electrode. Thus, if the metal will be etched away from these of particles, it may significantly reduce the number of shorting pinholes in the SU-8 layer. The etching solution also penetrated under the resist layer from the pinhole sites to form very small circular holes in the silver layer underneath the regions with no aluminium. These regions are observable with an optical microscope (see Fig 3.5). The back electrode bonding area was also left without aluminium. However, the silver can still provide an electrical contact to the back gate.

**Figure 3.5.** Circular regions etched in Al layer at the pinhole sites. Bright field optical micrograph, 20X

After removing the sample from the etching solution it was covered with one more layer of SU-8 with the same spinning parameters and put to the same etching solution one more time to ensure that silver was also removed from the particles. At this step the lithography process was not used and SU-8 covered full chip area, including back gate bonding area. Silver is etched more slowly than aluminium, and in this step it was etched only from the top of those particles, which were higher than the layer of SU-8. Also it can be noted that metal was etched from the particles much faster than from the planar area of the chip.

After etching procedures the chip was covered with a double layer of SU-8 and processed with electron beam lithography step once more to make an insulating layer of area 3mm by 3mm and thickness of 800nm.

#### 3.2.7 SINIS junction design and fabrication.

Electron beam lithography procedure was used to pattern the SINIS tunnel junction area and surrounding capacitor electrodes.

The lithography process consists of several steps: pattern design, photoresist deposition, exposure, resist development, structural material deposition and lift-off.

One very common pattern design for a single NIS junction contains two wires separated by a certain gap. During junction material deposition the first material is deposited at a certain angle, usually by physical vapor deposition. The other material layers are deposited at different angles, thus making different shadows of the pattern.

In the particular case of a double junction SINIS device made of aluminium and copper with native aluminium oxide as the insulating layer,  $\pi$ -shape of the structure was chosen. In this design, two lines of aluminium are deposited with a large evaporation angle along the lines, in order to make the shadow longer than the original pattern. After the oxidation procedure, copper is deposited perpendicular to the aluminium lines at a normal to the sample's plane.

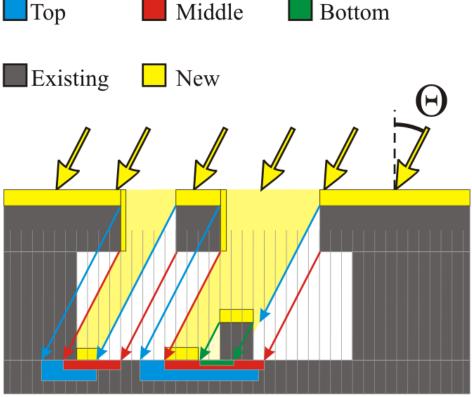

The positive resist used for shadowing, consists of by two layers, both sensitive to electron beam exposure, but the lower layer is more sensitive, which leads to an undercut structure. The undercut also leads to the formation of bridges of the top resist layer, which are needed for NIS tunnel junction formation (see Fig.3.6).

Figure 3.6. Schematic picture of the shadow evaporation technique.

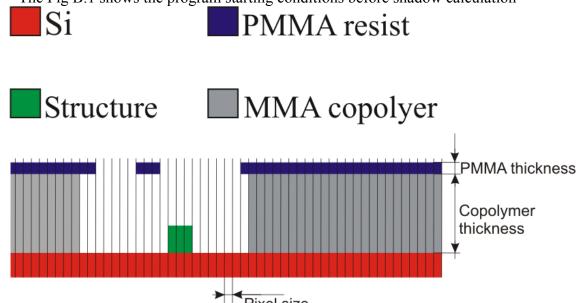

The complexity of the photoresist shape requires extensive and careful modeling. Pattern design usually requires 3D modeling of the deposition process, taking into account off-plane effects during shadow-evaporation.

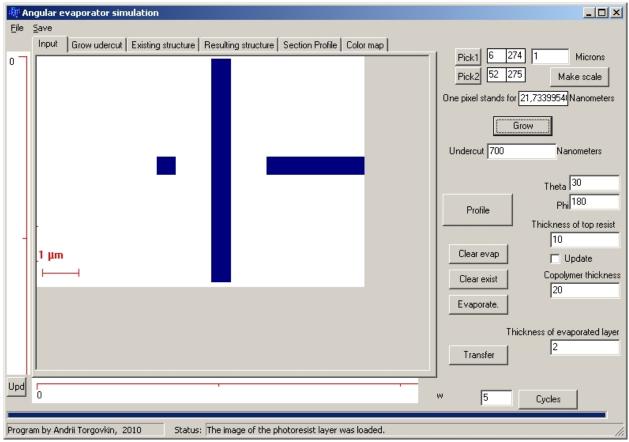

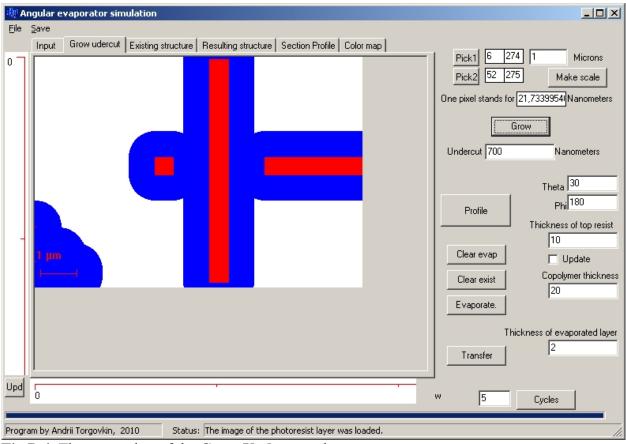

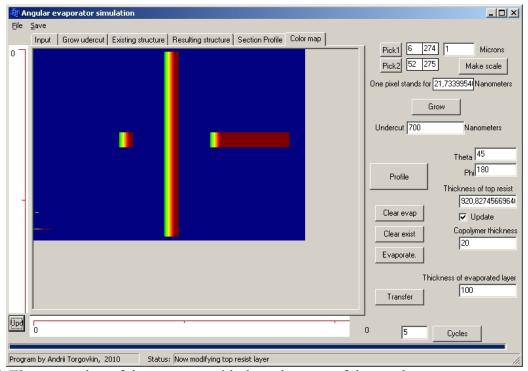

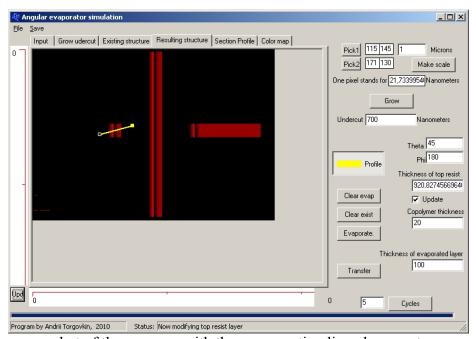

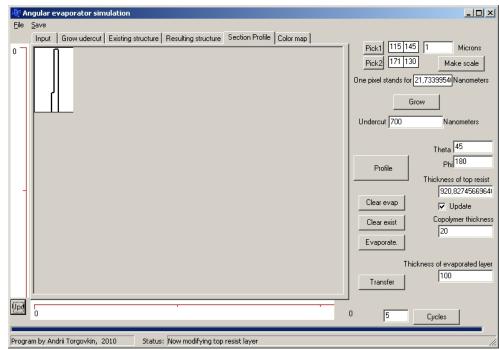

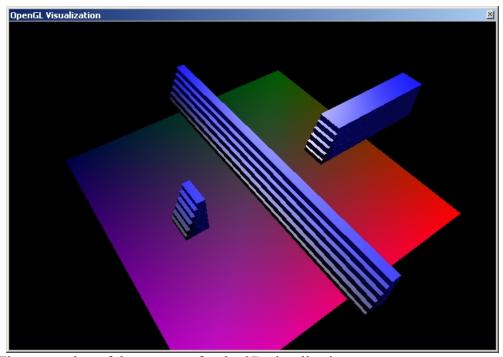

A computer program (see appendix B) for simulating shadow-evaporation was written and used to choose the optimal evaporation angles. The program allows the user to set the thickness of each of the two layers of the photoresist, and to set the azimuthal and polar angles of the sample plane normal with respect to the source of the deposited material. When the user loads the lithographic mask in the form of black-and-white picture, the program can start calculating the resulted evaporated structures of resist and deposited material. The resulted structures can be saved, loaded or processed further to model a sequential deposition processes. The program code is based on the raster ray tracing algorithm. This algorithm treats every pixel of input bitmap image in the same way, calculating whether there will be shadowing or not for an atom, which crosses the area of the pixel during the deposition process. Thus, the resolution of the method is one screen pixel of the input bitmap image. The calculation of the shadowing takes into account only that features of the sample, which are crossing the virtual trace of an atom that has to be deposited. In order to get a higher accuracy the user has to increase the absolute size (in pixels) of the processed lithographic mask picture. Instuctions for use of the program are given in the appendix B as well.

The EL9 methylmetacrylate copolymer (EL9, 9% solution of MMA in ethyl lactate) was used as the first, lower layer of electron beam resist with 500nm thickness. The chip was preheated for 1 minute at 160°C and after cool down to room temperature it was spin-coated by the polymer at 2500rpm for 45seconds. The second resist layer was a 1500nm of PMMA in A9 solution (9% solution of PMMA in anisole) spin-coated at 2500rpm, as well. Each resist layer was baked for 120 seconds after spin coating at 160°C

Prior to the exposure, the electron beam was focused on the substrate plane in a manual mode with the help of markers. Chip was intentionally contaminated by ultra fine silver powder with grain size up to 100nm. Powder aggregates of irregular shape and 1-1.5 micrometers size were chosen as markers and were imaged with the highest possible sharpness at the targeted exposure current parameters.

#### 3.2.8 Exposure

The lithography procedure was carried out with the Raith LEO 1430 scanning electron microscope.

Exposure took place in two steps. First, the SINIS junction area and the supply wires were exposed at a writefield of 512 x 512nm, area step size 72nm and current of 250pA. Next, the capacitor electrodes were exposed at lower precision: writefield 2048, area step size 312nm and 5nA current. Acceleration voltage and dose factor were set to 28kV and 130% respectively.

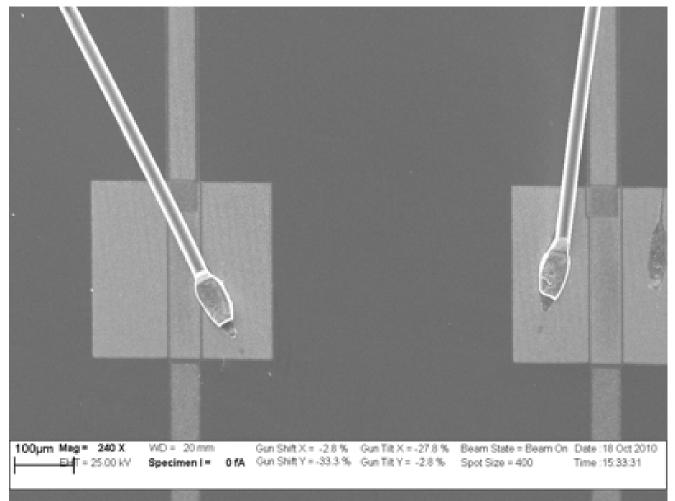

The capacitor electrodes themselves cannot be used as contact pads for connection of the sample to further wiring. The Al wire, which is usually welded to the contact pads by an ultrasonic bonder, will break through the insulating layer and short the capacitor. In order to avoid this, the bonding pads had to be fabricated in a following step on the region outside the SU-8 layer, with extra leads connected to the top capacitor electrodes. This leads have to step over the SU-8 edge, located 0.5mm away from the back electrode edge (see Fig. 3.1). Another minor reason to move bonding pads away from SU-8 is that Al wire tends to easily tear off the bonding pad, if it is located over the polymer (see Fig 3.7). The capacitor bonding pads were exposed at the same exposure session as the capacitor electrodes.

Connecting structures of 50 micrometers width with 300 by 300 micrometers bonding pads were patterned starting from capacitor electrodes (Fig 3.1), running over the 0.5mm region and going down to the region without any metal on it. So that, Al wires were bonded to connecting structures over the SiO2 (see Fig 3.7 – scanning electron micrograph of the bonding wires).

**Figure 3.7.** Scanning micrograph of bonding wires over the bonding pads of unsuccessful sample. The bonding pads were fabricated over the 200nm of SU-8 polymer, which caused Al wires easily to rip off together with deposited top electrode material.

#### 3.2.9 Development

The PMMA resist development was done, as usual, as a form of wet etching. First, the exposed chip was gently washed with 2-propanol (IPA) jet in order to wash away the silver powder contamination. After that, the sample was dried with a nitrogen gas jet, and it was put into the anisotropic developer (methyl isobutyl ketone (MIBK) dissolved in IPA) for 35seconds and then washed and dried again. All exposed areas of the sample were removed by the first developer and sharp lines with a thickness comparable with the height of the layer were formed (aspect ratio of nearly 1:1). Starting from this point, any contamination could be fatal for further performance of the sample, any airborne particle covering the line would restrict the uninterrupted conducting wire formation. Until the end of metal deposition process the sample had to be kept exposed to the cleanroom environment as short time as possible.

Next, the chip was put into the isotropic developer, which did not modify the top resist layer but made the bottom layer to expand the cavity and to form the undercut. The second developer takes only 6 seconds to etch a reasonable cavity. The second developer consists of methoxyethanol dissolved in methanol. This volatile solution could have easily over-etched the MMA copolymer, and thus required immediate IPA washing of the sample after development.

### 3.2.10 Metal deposition

Deposition of the material was done in the Ultra High Vacuum electron beam evaporator.

The chip was installed onto the sample holder in such a way that the two aluminium lines were oriented perpendicular to the axis of rotation. After insertion into the high vacuum environment, the sample was oriented at 75 degrees angle to the incident beam (Fig 3.8).

**Figure 3.8.** Aluminium deposition to the sample (schematics).

The evaporation took place at a rate of 0.2nm per second; 114nm of aluminium were deposited in total. If projected to the normal of the sample plane it would result in 29.5nm of height.

Next, the sample was placed into the loading chamber of the UHV for oxidation of the aluminium. Oxidation was done by introducing pure oxygen to the loading vacuum chamber at a pressure of 100mbar. Oxidation process lasted 310 seconds at room temperature [18].

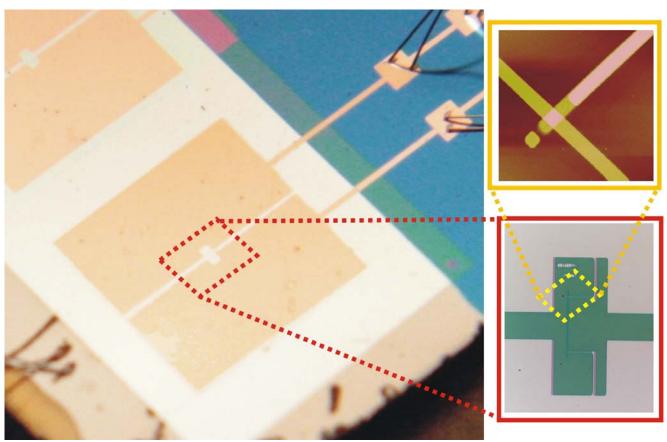

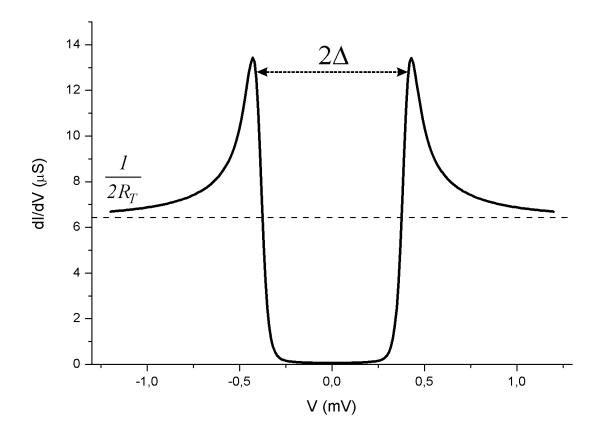

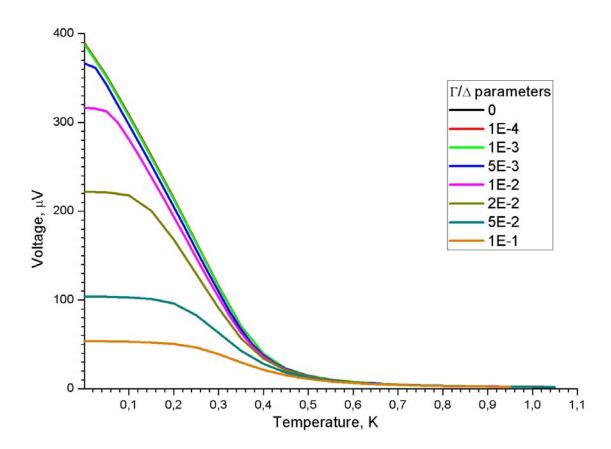

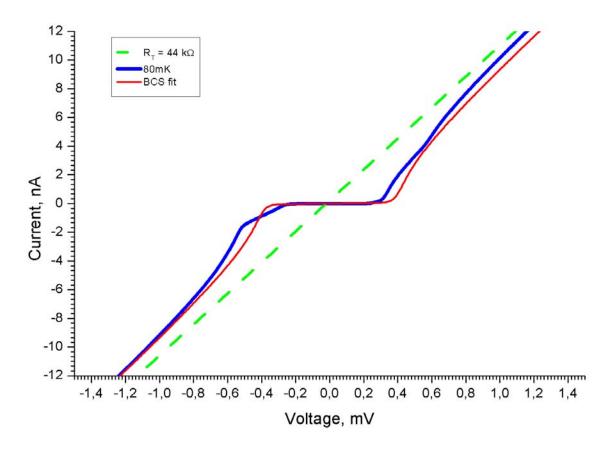

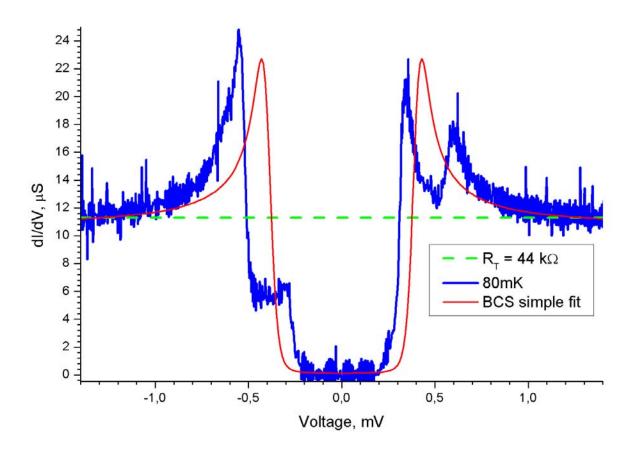

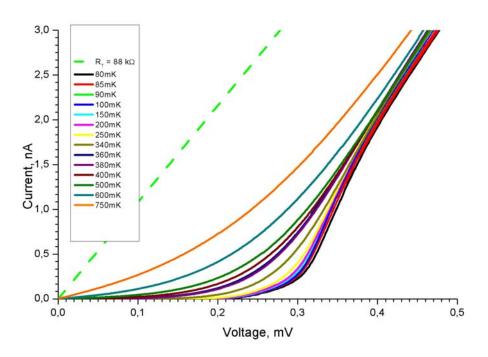

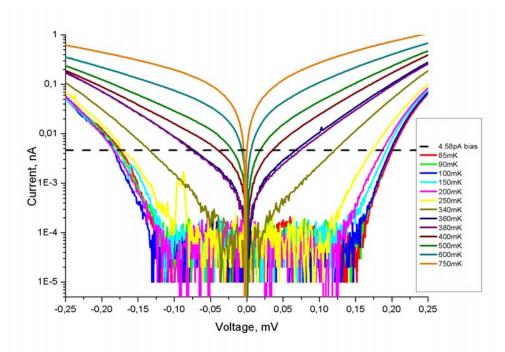

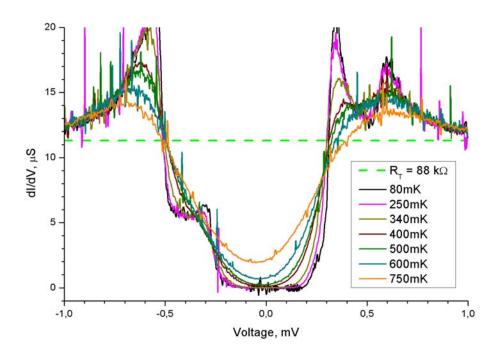

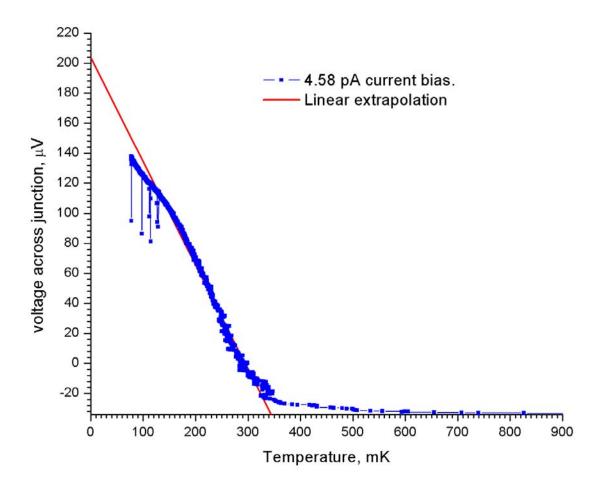

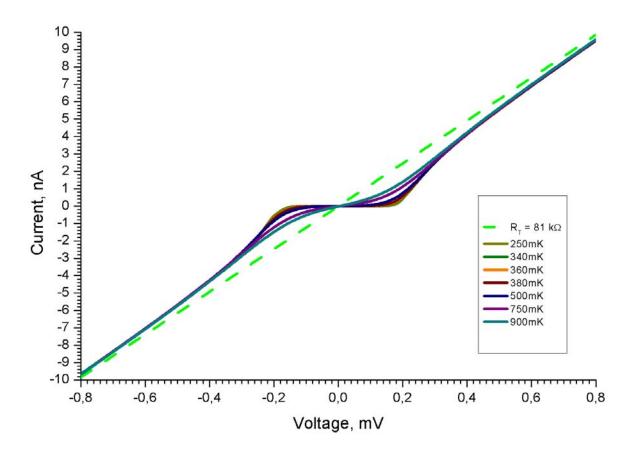

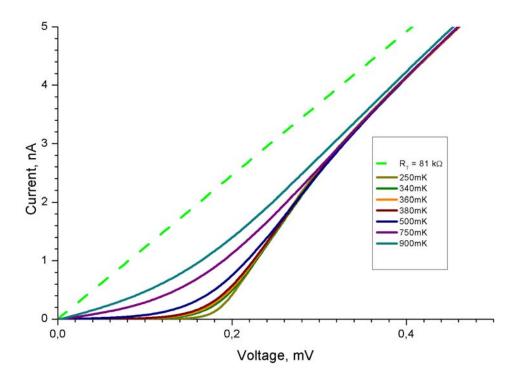

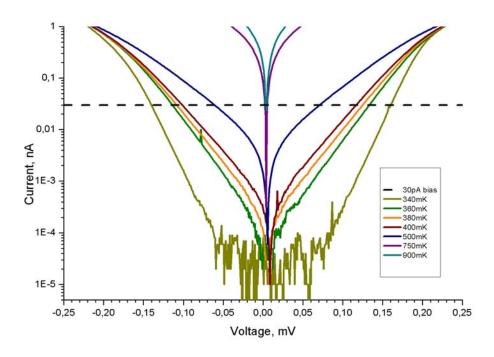

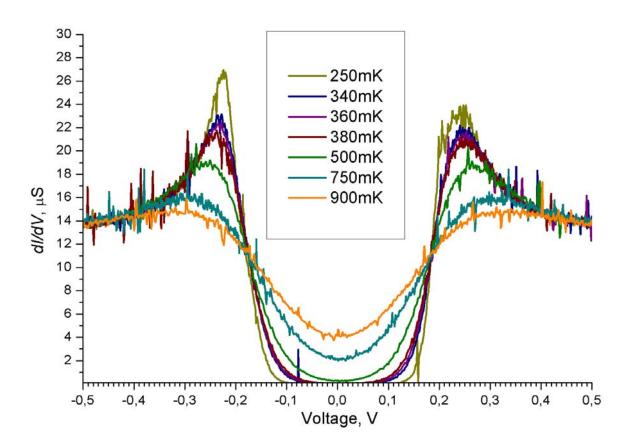

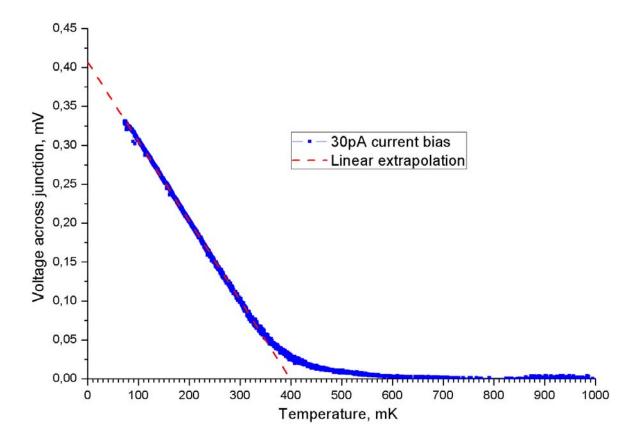

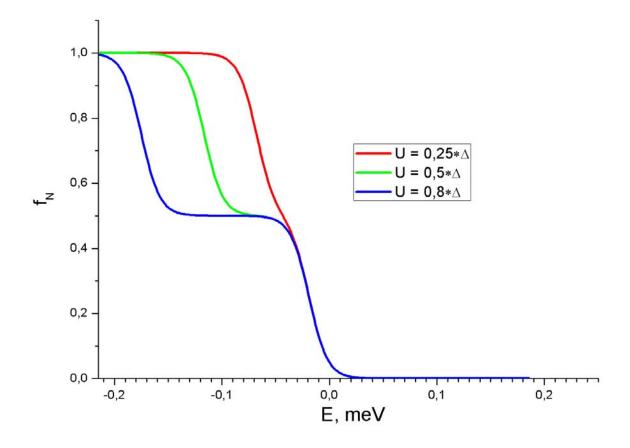

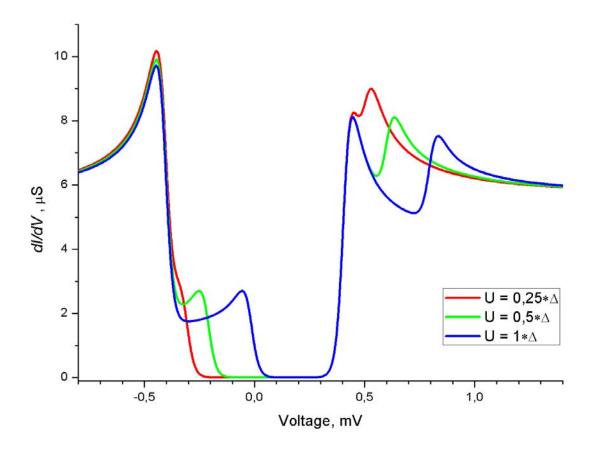

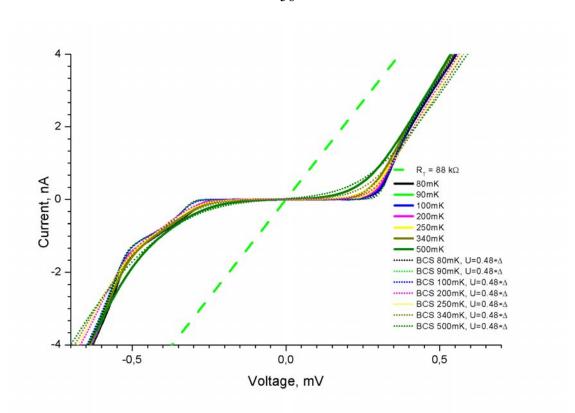

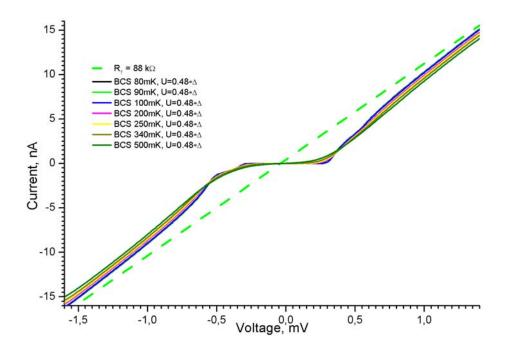

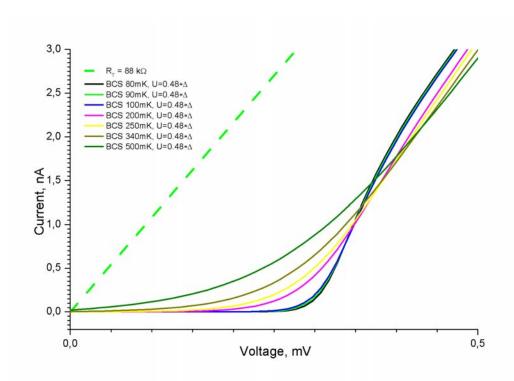

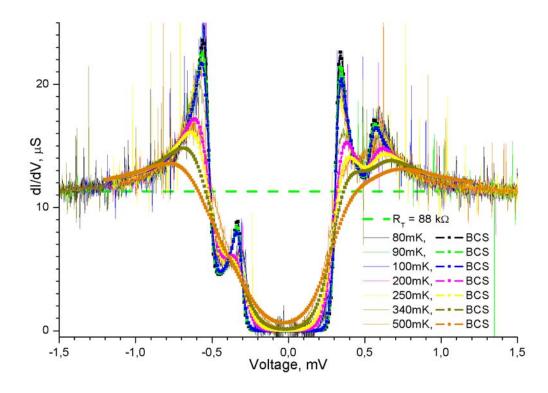

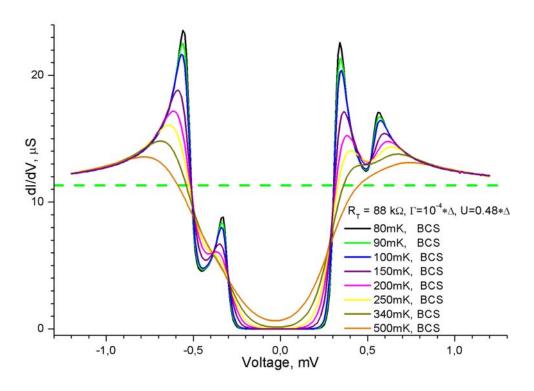

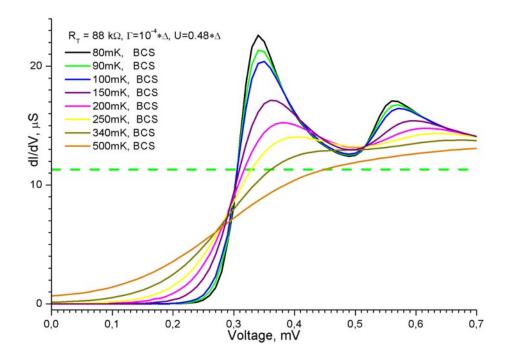

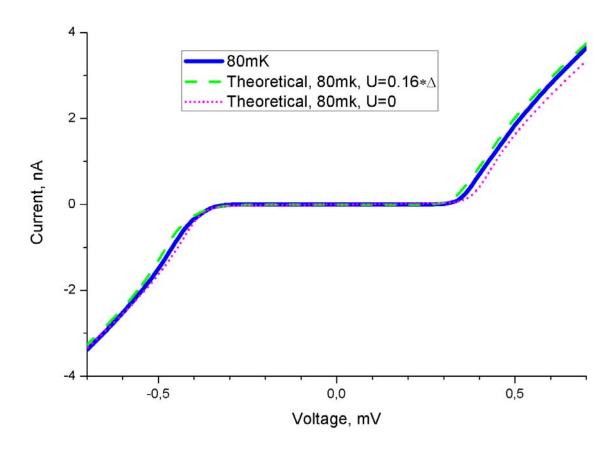

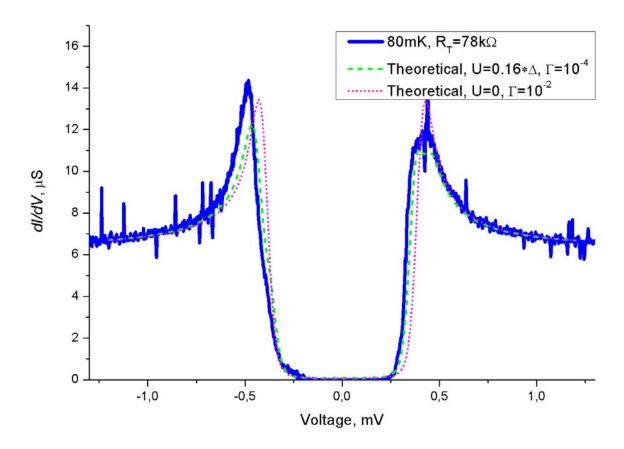

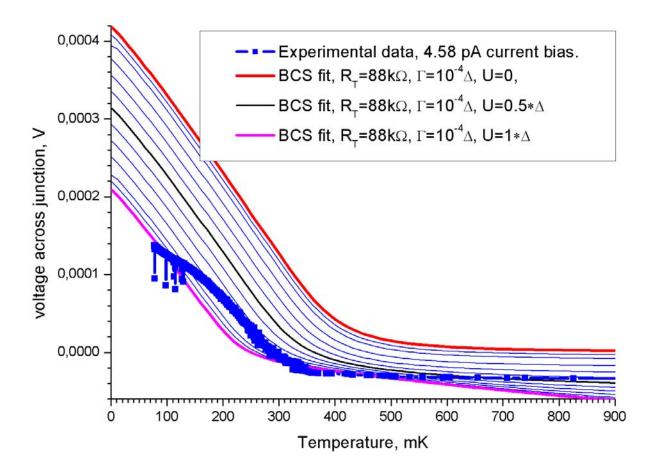

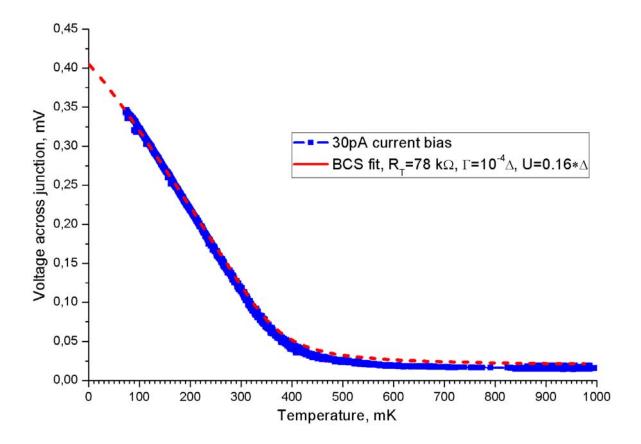

The normal conductor layer formation was done by deposition of 45nm of copper at a normal to the plane of the sample with the evaporation speed of 0.2nm per second. Copper layer was deposited over aluminium oxide and the cross-bar for the  $\pi$ -shape of the SINIS structure was formed.